- 您现在的位置:买卖IC网 > PDF目录98215 > TFP503PZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TFP503PZP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 13/27页 |

| 文件大小: | 624K |

| 代理商: | TFP503PZP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

TFP503

PanelBus HDCP DIGITAL RECEIVER

SLDS149 AUGUST 2004

20

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

I2C interface (continued)

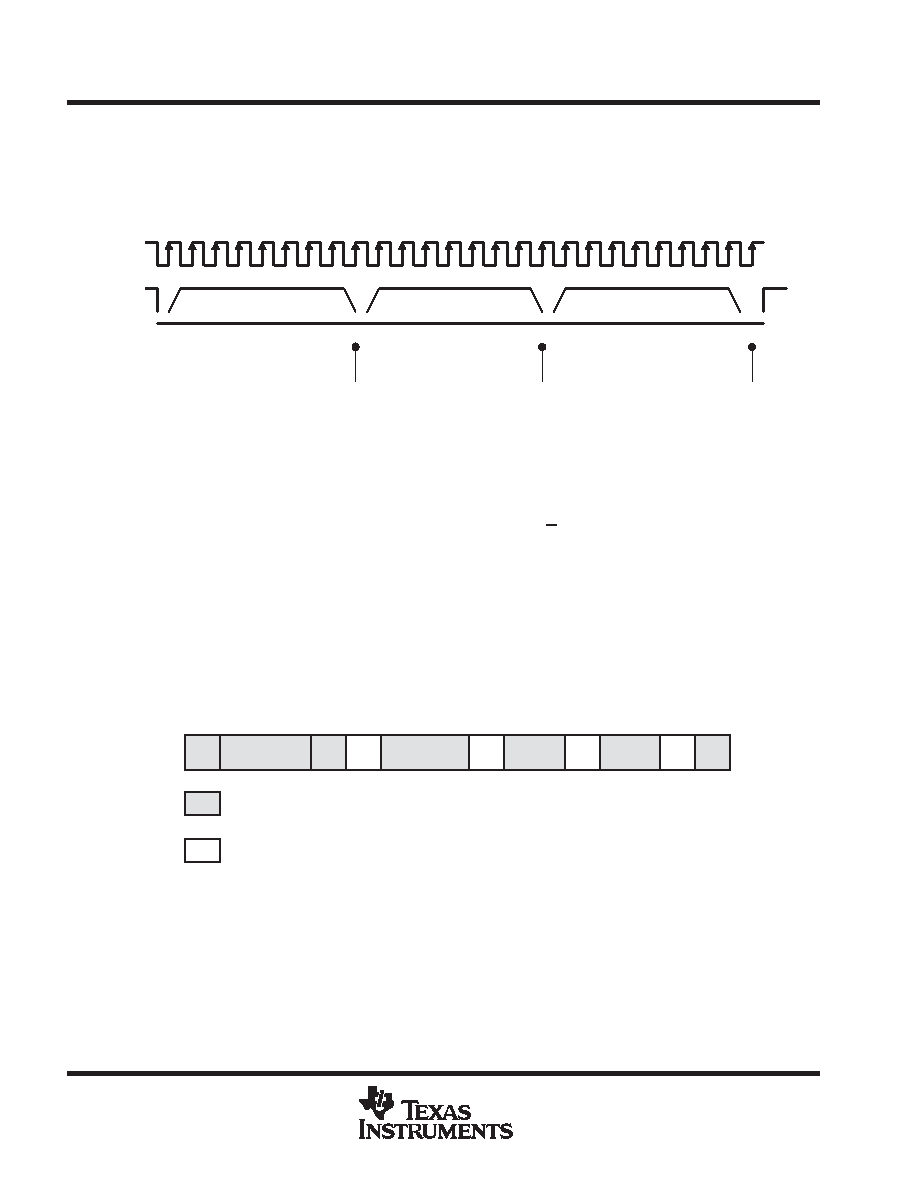

The start and stop conditions are shown in Figure 16. The high-to-low transition of DDC_SDA while DDC_SCL

is high defines the start condition. The low-to-high transition of DDC_SDA while DDC_SCL is high defines the

stop condition. Each cycle (data or address) consists of 8 bits of serial data followed by 1 acknowledge bit

generated by the receiving device. Thus, each data/address cycle contains 9 bits as shown in Figure 17.

DDC_SCL

1

2

3

4

5

6

7

8

9

DDC_SDA

1

2

3

4

5

6

7

8

9

2

3

4

5

6

7

1

Slave Address

MSB

Sub Address

Data

Stop

Figure 17. I2C Access Cycles

Following a start condition, each I2C device decodes the slave address. The TFP503 responds with an

acknowledge by pulling the DDC_SDA line low during the ninth clock cycle if it decodes the address as its

address. During subsequent subaddress and data cycles, the TFP503 responds with an acknowledge as shown

in Figure 18. The subaddress is autoincremented after each data cycle.

The transmitting device must not drive the DDC_SDA signal during the acknowledge cycle so that the receiving

device may drive the DDC_SDA signal low. The not acknowledge, A, condition is indicated by the master by

keeping the DDC_SDA signal high just before it asserts the stop, P, condition. This sequence terminates a read

cycle as shown in Figure 19.

The slave address consists of 7 bits of address along with 1 bit of read/write information as shown below in

Figures 18, 19, and 20. For the TFP503, the possible slave addresses (including the R/W bit) are 0x74, 0x76

for write cycles and 0x75 and 0x77 for read cycles. Refer to the register map section for additional base address

information.

In order to minimize the number of bits that must be transferred for the link integrity check, a second read format

is supported. This format, shown in Figure 20, has an implicit subaddress equal to 0x08, the starting location

of Ri’.

Data

S

Slave Address

Sub Address

A

W

P

From Transmitter

From Receiver

W

Write

A

Acknowledge

S

Start Condition

P

Stop Condition

A

Data

A

Figure 18. I2C Write Cycle

相关PDF资料 |

PDF描述 |

|---|---|

| TFP510PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP510PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP6422PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TFP503PZPG4 | 制造商:Texas Instruments 功能描述:DGTL RCVR 1RX 100HTQFP - Rail/Tube |

| TFP50N06 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 50A, 60V, 0.023Ω |

| TFP510 | 制造商:TI 制造商全称:Texas Instruments 功能描述:TI PANEL BUS DIGITAL TRANSMITTER |

| TFP510PAPG4 | 制造商:Texas Instruments 功能描述:PNLBUS DGTL TRANSMITTER 64HTQFP - Rail/Tube |

| TFP513 | 制造商:TI 制造商全称:Texas Instruments 功能描述:TI PANELBUS DIGITAL TRANSMITTER |

发布紧急采购,3分钟左右您将得到回复。