- 您现在的位置:买卖IC网 > PDF目录98215 > TFP503PZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TFP503PZP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 22/27页 |

| 文件大小: | 624K |

| 代理商: | TFP503PZP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页

TFP503

PanelBus HDCP DIGITAL RECEIVER

SLDS149 AUGUST 2004

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

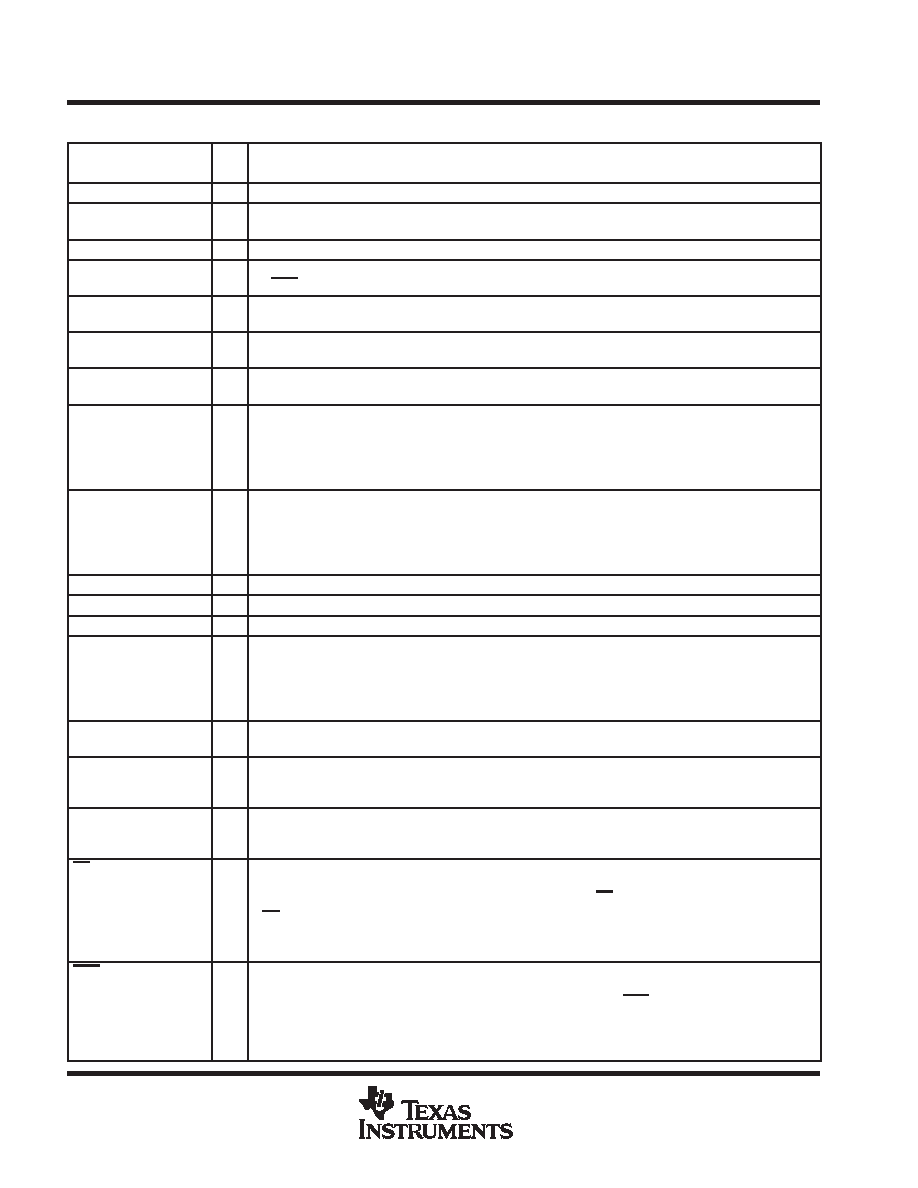

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

AGND

79

Analog ground. Ground reference and current return for analog circuitry.

AVDD

82, 85,

88, 91

Analog VDD. Power supply for analog circuitry. Nominally 3.3 V.

CAP

67

O

Bypass capacitor. 4.7-

F tantalum and 0.01-F ceramic capacitors connected to ground.

CTL[2:1]

41, 40

O

General-purpose control signals. Used for user-defined control. In normal mode, CTL1 is not powered down

via PDO.

DDC_SA

94

I

Display data channel_serial address. I2C slave address bit A0 for display data channel (DDC). Refer to I2C

interface section for more details.

DDC_SCL

92

I/O

Display data channel_serial clock. I2C clock for the DDC. This terminal is 3.3-V tolerant and typically sinks

3 mA. External pullup resistors are required. A level translator must be used to interface to 5-V DDC lines.

DDC_SDA

93

I/O

Display data channel_serial data. I2C data for the DDC. This terminal is 3.3-V tolerant and typically sinks

3 mA. External pullup resistors are required. A level translator must be used to interface to 5-V DDC lines.

DE

46

O

Output data enable. Indicates time of active video display versus nonactive display or blanking interval. During

blanking, only HSYNC, VSYNC, and CTL[2:1] are transmitted. During times of active display, or nonblanking,

only pixel data, QE[23:0] and QO[23:0], is transmitted.

High: active display interval

Low: blanking interval

DFO

1

I

Output clock data format. Controls the output clock (ODCK) format for either TFT or DSTN panel support. For

TFT support, the ODCK clock runs continuously. For DSTN support, the ODCK only clocks when DE is high;

otherwise, ODCK is held low when DE is low.

High: DSTN support/ODCK held low when DE is low.

Low: TFT support/ODCK runs continuously.

DGND

5, 39, 68

Digital ground. Ground reference and current return for digital core.

DVDD

6, 38

Digital VDD. Power supply for digital core. Nominally 3.3 V.

HSYNC

48

O

Horizontal sync output

OCK_INV

100

I

ODCK polarity. Selects the ODCK edge on which pixel data (QE[23:0] and QO[23:0]) and control signals

(HSYNC, VSYNC, DE, CTL[2:1]) are latched.

Normal mode:

High: latches output data on rising ODCK edge.

Low: latches output data on falling ODCK edge.

ODCK

44

O

Output data clock. Pixel clock. All pixel outputs QE[23:0] and QO[23:0] (if in 2-pixel/clock mode) along with

DE, HSYNC, VSYNC, and CTL[2:1] are synchronized to this clock.

OGND

19, 28,

45, 58,

76

Output driver ground. Ground reference and current return for digital output drivers.

OVDD

18, 29,

43, 57,

78

Output driver VDD. Power supply for output drivers. Nominally 3.3 V.

PD

2

I

Power down. An active low signal that controls the TFP503 power-down state. During power down, all output

buffers are switched to a high-impedance state and brought low through a weak pulldown resistor. All analog

circuits are powered down and all inputs are disabled, except for PD.

If PD is left unconnected, an internal pullup resistor defaults the TFP503 to normal operation.

High: normal operation

Low: power down

PDO

9

I

Output drive power down. An active low signal that controls the power-down state of the output drivers. During

output drive power down, the output drivers (except SCDT and CTL1) are driven to a high-impedance state. A

weak pulldown resistor slowly pulls these outputs to a low level. When PDO is left unconnected, an internal

pullup resistor defaults the TFP503 to normal operation.

High: normal operation/output drivers on

Low: output drive power down

相关PDF资料 |

PDF描述 |

|---|---|

| TFP510PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP510PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP513PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| TFP6422PAP | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TFP503PZPG4 | 制造商:Texas Instruments 功能描述:DGTL RCVR 1RX 100HTQFP - Rail/Tube |

| TFP50N06 | 制造商:TAK_CHEONG 制造商全称:Tak Cheong Electronics (Holdings) Co.,Ltd 功能描述:N-Channel Power MOSFET 50A, 60V, 0.023Ω |

| TFP510 | 制造商:TI 制造商全称:Texas Instruments 功能描述:TI PANEL BUS DIGITAL TRANSMITTER |

| TFP510PAPG4 | 制造商:Texas Instruments 功能描述:PNLBUS DGTL TRANSMITTER 64HTQFP - Rail/Tube |

| TFP513 | 制造商:TI 制造商全称:Texas Instruments 功能描述:TI PANELBUS DIGITAL TRANSMITTER |

发布紧急采购,3分钟左右您将得到回复。