- 您现在的位置:买卖IC网 > PDF目录98252 > TLV320AIC22PT (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF资料下载

参数资料

| 型号: | TLV320AIC22PT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封装: | ROHS COMPLIANT, PLASTIC, LQFP-48 |

| 文件页数: | 16/55页 |

| 文件大小: | 782K |

| 代理商: | TLV320AIC22PT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

TLV320AIC22

DUAL VOIP CODEC

SLAS281B – JULY 2000 – REVISED JUNE 2002

23

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

control register address and data (continued)

0

1

8

7

654

32

10

11

12

13

14

15

9

MSB

LSB

Control Register Data

Unused

NOTES: A. If the register address is 0x00h, then no register will be updated.

B. The default condition is for control information to be updated every frame. If control information is not to be updated every frame,

then register 17 can be programmed to cause the control slots to appear with N frames of empty control slots between them. The

contents of register 17 is equal to N. In this condition, the data in slots 0 and 1 that appear in the N frames between frames with valid

control slots are ignored. The default setting for register 17 is 0; control slots will appear in every frame. After register 17 is

programmed with a nonzero value, the first sequence will have N – 1 frames with empty control slots.

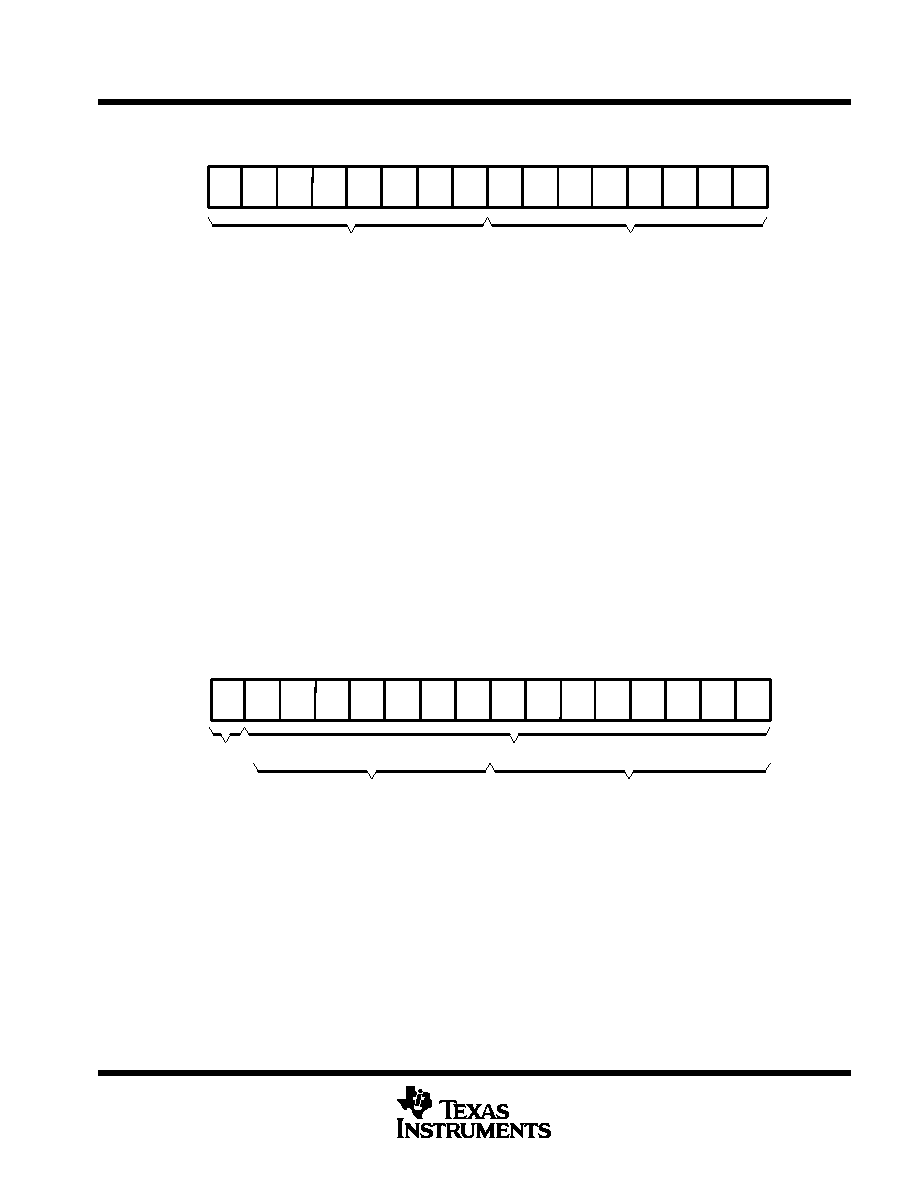

Figure 6. Bit Assignment and Definition for Slot-1 Word

ADC data word

A data word occupies one time slot and is 16 bits long. The ADC data word (output on DOUT) can be any of

the following:

D Data-valid flag + 15 bits of linear data

D 16 bits of linear data (no data-valid flag)

D Data-valid flag + A-law or -law coded PCM data

D A-law or -law coded PCM data (no data-valid flag)

The selection of linear, A-law, or

-law coding is programmed in register 15, bits 6 and 7. The selection for

providing the data-valid flag bit is programmed in register 13. See the ADC and DAC channel data section for

a detailed description of the valid and invalid data.

The structure of a data word is shown in Figure 7 and Figure 8.

0

1

8

7

654

32

10

11

12

13

14

15

9

Data-Valid

Flag Bit

15-Bit Codec Data, (Linear Mode)

MSB

LSB

NOTE: The MSB of the codec data is bit 14 for linear mode and bit 7 for A-law and

-law.

8-Bit Codec Data (A-Law,

-Law PCM Mode)

Zeros When A-Law or

-Law PCM

Mode Selected

Figure 7. Bit Assignment and Definition for ADC Data Word When the Data-Valid Flag is Enabled

Figure 7 describes the ADC data-word format when the data-valid flag is used. The data-valid flag is positioned

in bit 15 (the MSB of the data word) and is transmitted first. The flag bit is enabled by programming register 13.

Bit 14 of the data word is the most significant bit of the 15-bit codec data when the linear mode is selected and

the data-valid flag is enabled.

When A-law or

-law PCM coding is selected, the 8 bits of the PCM data are located, with the MSB in the bit 7

location and the LSB in the bit 0 location of the data word. Unused bits are zero when PCM coding is enabled.

Bit 15 always is the data-valid flag for both the PCM and linear coding when the data-valid flag is enabled. The

selection of linear, A-law, or

-law coding is programmed in register 15, bits 6 and 7.

相关PDF资料 |

PDF描述 |

|---|---|

| TLV320AIC22PTR | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC23BGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC23BIPW | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| TLV320AIC23BPW | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV320AIC22PTR | 功能描述:接口—CODEC DUAL VOIP CODEC RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC23 | 制造商:TI 制造商全称:Texas Instruments 功能描述:STereo Audio CODEC, 8- to 96kHz, With Integrated Headphone Amplifier |

| TLV320AIC23_06 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B | 制造商:TI 制造商全称:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23B_06 | 制造商:TI 制造商全称:Texas Instruments 功能描述:Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

发布紧急采购,3分钟左右您将得到回复。