- 您现在的位置:买卖IC网 > PDF目录98271 > TPA2016D2RTJT (TEXAS INSTRUMENTS INC) 2.8 W, 2 CHANNEL, AUDIO AMPLIFIER, PQCC20 PDF资料下载

参数资料

| 型号: | TPA2016D2RTJT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 音频/视频放大 |

| 英文描述: | 2.8 W, 2 CHANNEL, AUDIO AMPLIFIER, PQCC20 |

| 封装: | 4 X 4 MM, GREEN, PLASTIC, QFN-20 |

| 文件页数: | 14/38页 |

| 文件大小: | 1216K |

| 代理商: | TPA2016D2RTJT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

MULTIPLE-BYTE WRITE AND INCREMENTAL MULTIPLE-BYTE WRITE

Register

SINGLE-BYTE READ

A6

A5

A0 R/W ACK A7

A6

A5

A4

A0 ACK

A6

A5

A0

ACK

Start

Condition

Stop

Condition

Acknowledge

I2CDeviceAddressand

Read/WriteBit

Register

DataByte

D7

D6

D1

D0 ACK

I2CDeviceAddressand

Read/WriteBit

Not

Acknowledge

R/W

A1

RepeatStart

Condition

MULTIPLE-BYTE READ

A6

A0

ACK

Acknowledge

I2CDeviceAddressand

Read/WriteBit

R/W

A6

A0

R/W ACK

A0 ACK

D7

D0

ACK

Start

Condition

Stop

Condition

Acknowledge

LastDataByte

ACK

FirstDataByte

RepeatStart

Condition

Not

Acknowledge

I2CDeviceAddressand

Read/WriteBit

Register

OtherDataBytes

A7

A6

A5

D7

D0 ACK

Acknowledge

D7

D0

www.ti.com........................................................................................................................................................ SLOS524D – JUNE 2008 – REVISED AUGUST 2009

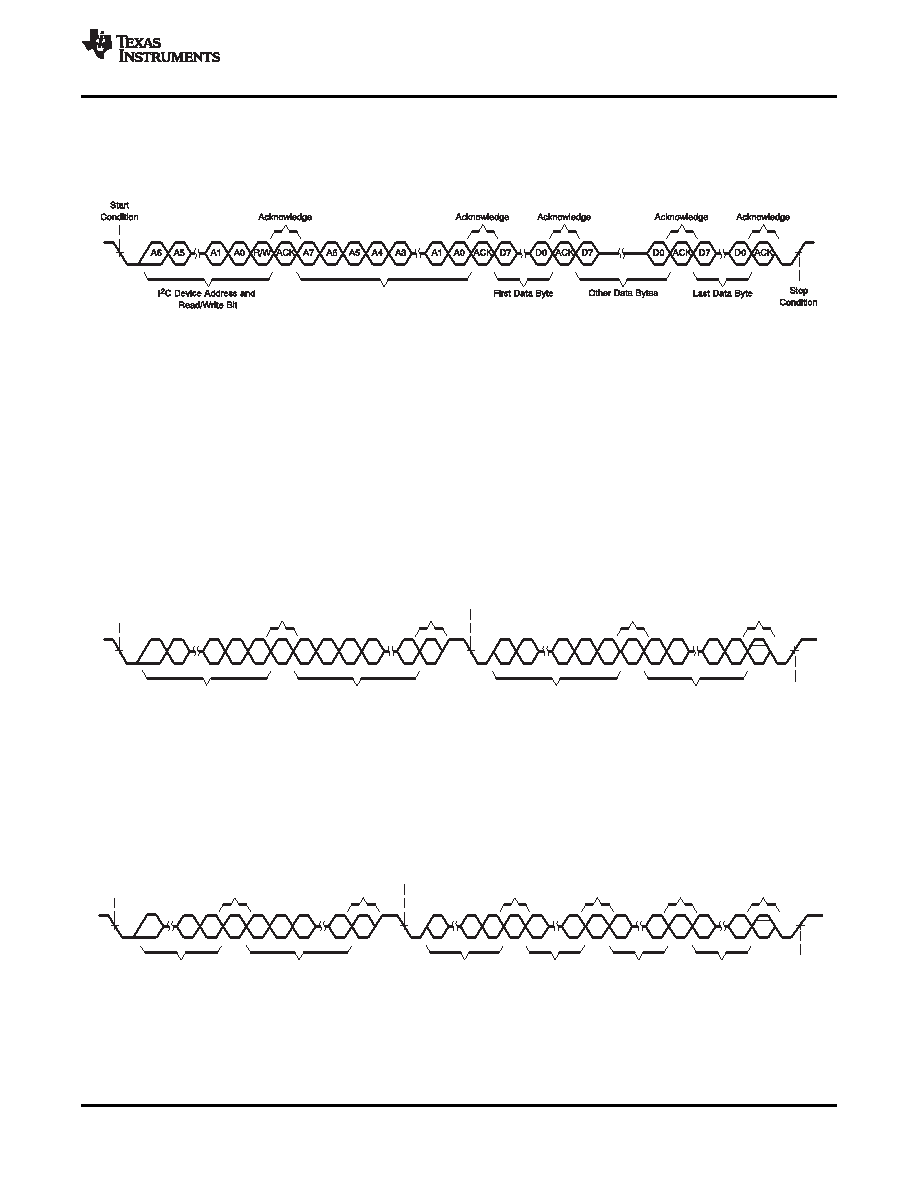

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes

are transmitted by the master device to the TPA2016D2 as shown in Figure 38. After receiving each data byte,

the TPA2016D2 responds with an acknowledge bit.

Figure 38. Multiple-Byte Write Transfer

As Figure 39 shows, a single-byte data read transfer begins with the master device transmitting a start condition

followed by the I2C device address and the read/write bit. For the data read transfer, both a write followed by a

read are actually executed. Initially, a write is executed to transfer the address byte of the internal memory

address to be read. As a result, the read/write bit is set to a '0'.

After receiving the TPA2016D2 address and the read/write bit, the TPA2016D2 responds with an acknowledge

bit. The master then sends the internal memory address byte, after which the TPA2016D2 issues an

acknowledge bit. The master device transmits another start condition followed by the TPA2016D2 address and

the read/write bit again. This time the read/write bit is set to '1', indicating a read transfer. Next, the TPA2016D2

transmits the data byte from the memory address being read. After receiving the data byte, the master device

transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer.

Figure 39. Single-Byte Read Transfer

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes

are transmitted by the TPA2016D2 to the master device as shown in Figure 40. With the exception of the last

data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 40. Multiple-Byte Read Transfer

Copyright 2008–2009, Texas Instruments Incorporated

21

Product Folder Link(s): TPA2016D2

相关PDF资料 |

PDF描述 |

|---|---|

| TPA2017D2RTJR | 2.8 W, 2 CHANNEL, AUDIO AMPLIFIER, PQCC20 |

| TPA2017D2RTJT | 2.8 W, 2 CHANNEL, AUDIO AMPLIFIER, PQCC20 |

| TPA2026D2YZHR | AUDIO AMPLIFIER, PBGA16 |

| TPA2026D2YZHT | AUDIO AMPLIFIER, PBGA16 |

| TPA2028D1YZFR | 3 W, 1 CHANNEL, AUDIO AMPLIFIER, PBGA9 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPA2016D2V1YZHR | 制造商:Texas Instruments 功能描述: |

| TPA2016D2YZHR | 功能描述:音频放大器 1.7W/Ch Stereo Class D Aud Amp RoHS:否 制造商:STMicroelectronics 产品:General Purpose Audio Amplifiers 输出类型:Digital 输出功率: THD + 噪声: 工作电源电压:3.3 V 电源电流: 最大功率耗散: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:TQFP-64 封装:Reel |

| TPA2016D2YZHT | 功能描述:音频放大器 1.7W/Ch Stereo Class D Aud Amp RoHS:否 制造商:STMicroelectronics 产品:General Purpose Audio Amplifiers 输出类型:Digital 输出功率: THD + 噪声: 工作电源电压:3.3 V 电源电流: 最大功率耗散: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:TQFP-64 封装:Reel |

| TPA2016DYZHT2 | 制造商:Texas Instruments 功能描述: |

| TPA2017D2 | 制造商:TI 制造商全称:Texas Instruments 功能描述:2.8-W/Ch Stereo Class-D Audio Amplifier with SmartGainTM Dynamic Range Compression and AGC |

发布紧急采购,3分钟左右您将得到回复。