- 您现在的位置:买卖IC网 > PDF目录98274 > TPA5050RSAT (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC16 PDF资料下载

参数资料

| 型号: | TPA5050RSAT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| 封装: | 4 X 4 MM, GREEN, PLASTIC, QFN-16 |

| 文件页数: | 2/21页 |

| 文件大小: | 784K |

| 代理商: | TPA5050RSAT |

www.ti.com

SERIAL CONTROL INTERFACE REGISTER SUMMARY

CONTROL REGISTER (0x01)

AUDIO DELAY REGISTERS (0x02–0x05)

FRAME DELAY REGISTERS (0x06)

SLOS492B – MAY 2006 – REVISED MAY 2007

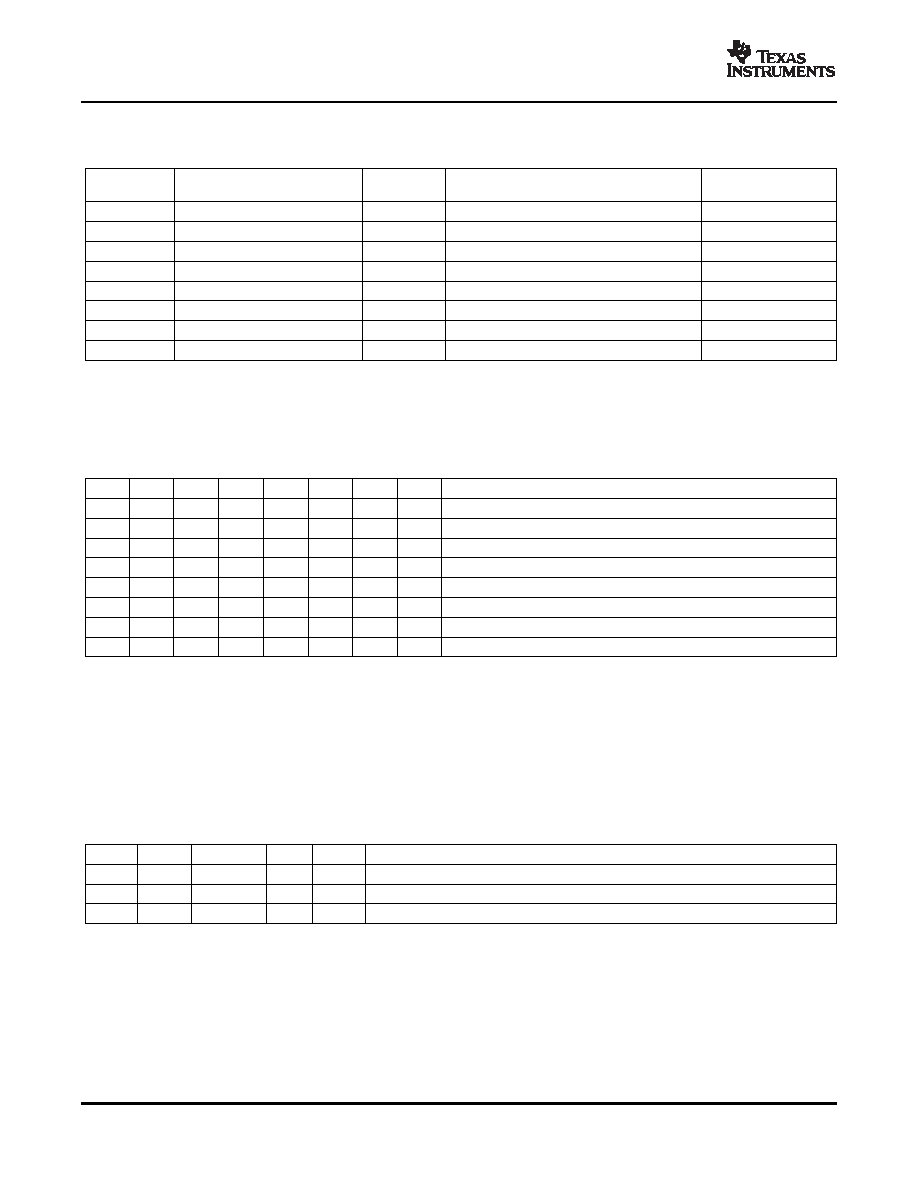

Table 2. Serial Control Register Summary

REGISTER

REGISTER NAME

NO. OF

CONTENTS

INITIALIZATION

BYTES

VALUE

0x01

Control Register

1

Description shown in subsequent section

00

0x02

Right Delay Upper (5 bits)

1

Description shown in subsequent section

00

0x03

Right Delay Lower (8 bits)

1

Description shown in subsequent section

00

0x04

Left Delay Upper (5 bits)

1

Description shown in subsequent section

00

0x05

Left Delay Lower (8 bits)

1

Description shown in subsequent section

00

0x06

Frame Delay

1

Description shown in subsequent section

00

0x07

RJ Packet Length

1

Description shown in subsequent section

00

0x08

Complete Update

1

Description shown in subsequent section

00

The control register allows the user to mute a specific audio channel. It is also used to specify the data type (I2S,

Right-Justified, or Left-Justified.

Table 3. Control Registers (0x01)(1)

D7

D6

D5

D4

D3

D2

D1

D0

FUNCTION

0

X

–

Left and Right channel are active.

0

1

X

–

Left channel is MUTED.

1

0

X

–

Right channel is MUTED.

1

X

–

Left and Right channel are MUTED.

–

X

0

I2S data format

–

X

0

1

Right-justified data format (see PACKET LENGTH register 0x07)

–

X

1

0

Left-justified data format

–

X

1

Bypass mode – data is passed straight through without delay.

(1)

Default values are in bold.

The audio delay for the left and right channels is fixed by writing a total of 13 bits (2 byte transfer) to upper and

lower registers as specified in Table 1. A multiple byte transfer should be performed starting with the control

register and following with 4 bytes to fill the upper and lower registers associated with right/left channel delay.

The decimal value of D0–D12 equals the number of samples to delay. The maximum number of delayed

samples is 8191 for the TPA5050. This equates to 170.65 ms [8191

× (1/fs)] at 48 kHz.

Table 4. Audio Delay Registers (0x02–0x05)(1)

D12

D11

D10–D2

D1

D0

FUNCTION

0

Left and Right audio is passed to output with no delay.

0

1

Left and Right audio is delayed by 1 sample (1/fs = delay time)

1

Left and Right audio is delayed by 8191 samples (8191/fs = delay time)

(1)

Default values are in bold.

This register can be used to specify delay in video frames instead of audio samples. When the MSB is set to 1,

the audio delay registers (0x01–0x04) are bypassed and the Frame Delay Register is used to set the delay

based on the frame rate (D6), audio sample rate (D5–D3), and number of frames to delay (D2–D0).

The total audio delay time is calculated by the following formula:

Audio Delay (in samples) = int [# Delay Frames

× (1/Frame Rate) × Audio Sample Rate]

10

相关PDF资料 |

PDF描述 |

|---|---|

| TPA5051RSARG4 | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TPA5051RSAR | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TPA5051RSATG4 | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TPA5051RSAT | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TPA6011A4PWPR | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPA5050RSATG4 | 功能描述:音频 DSP St Dig Aud Delay Proc RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TPA5051 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FOUR CHANNEL DIGITAL AUDIO LIP-SYNC DELAY WITH I2C CONTROL |

| TPA5051_07 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FOUR CHANNEL DIGITAL AUDIO LIP-SYNC DELAY WITH I2C CONTROL |

| TPA5051EVM | 功能描述:音频 IC 开发工具 AUD DELAY DEVICE RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| TPA5051RSAR | 功能描述:音频 DSP 4Ch Dig Aud Delay Proc RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。