- 您现在的位置:买卖IC网 > PDF目录69512 > TPS54615PWPRG4 (TEXAS INSTRUMENTS INC) 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 PDF资料下载

参数资料

| 型号: | TPS54615PWPRG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 稳压器 |

| 英文描述: | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| 封装: | GREEN, PLASTIC, HTSSOP-28 |

| 文件页数: | 5/23页 |

| 文件大小: | 706K |

| 代理商: | TPS54615PWPRG4 |

TPS54611, TPS54612

TPS54613, TPS54614

TPS54615, TPS54616

SLVS400C AUGUST 2001 REVISED APRIL 2005

www.ti.com

13

DETAILED DESCRIPTION

Under Voltage Lock Out (UVLO)

The TPS5461x incorporates an under voltage lockout

circuit to keep the device disabled when the input voltage

(VIN) is insufficient. During power up, internal circuits are

held inactive until VIN exceeds the nominal UVLO

threshold voltage of 2.95 V. Once the UVLO start threshold

is reached, device start-up begins. The device operates

until VIN falls below the nominal UVLO stop threshold of

2.8 V. Hysteresis in the UVLO comparator, and a 2.5-s

rising and falling edge deglitch circuit, reduces the

likelihood of shutting the device down due to noise on VIN.

Slow-Start/Enable (SS/ENA)

The slow-start/enable pin provides two functions. First, the

pin acts as an enable (shutdown) control by keeping the

device turned off until the voltage exceeds the start

threshold voltage of approximately 1.2 V. When SS/ENA

exceeds the enable threshold, device start up begins. The

reference voltage fed to the error amplifier is linearly

ramped up from 0 V to 0.891 V in 3.35 ms. Similarly, the

converter output voltage reaches regulation in

approximately 3.35 ms. Voltage hysteresis and a 2.5-s

falling edge deglitch circuit reduce the likelihood of

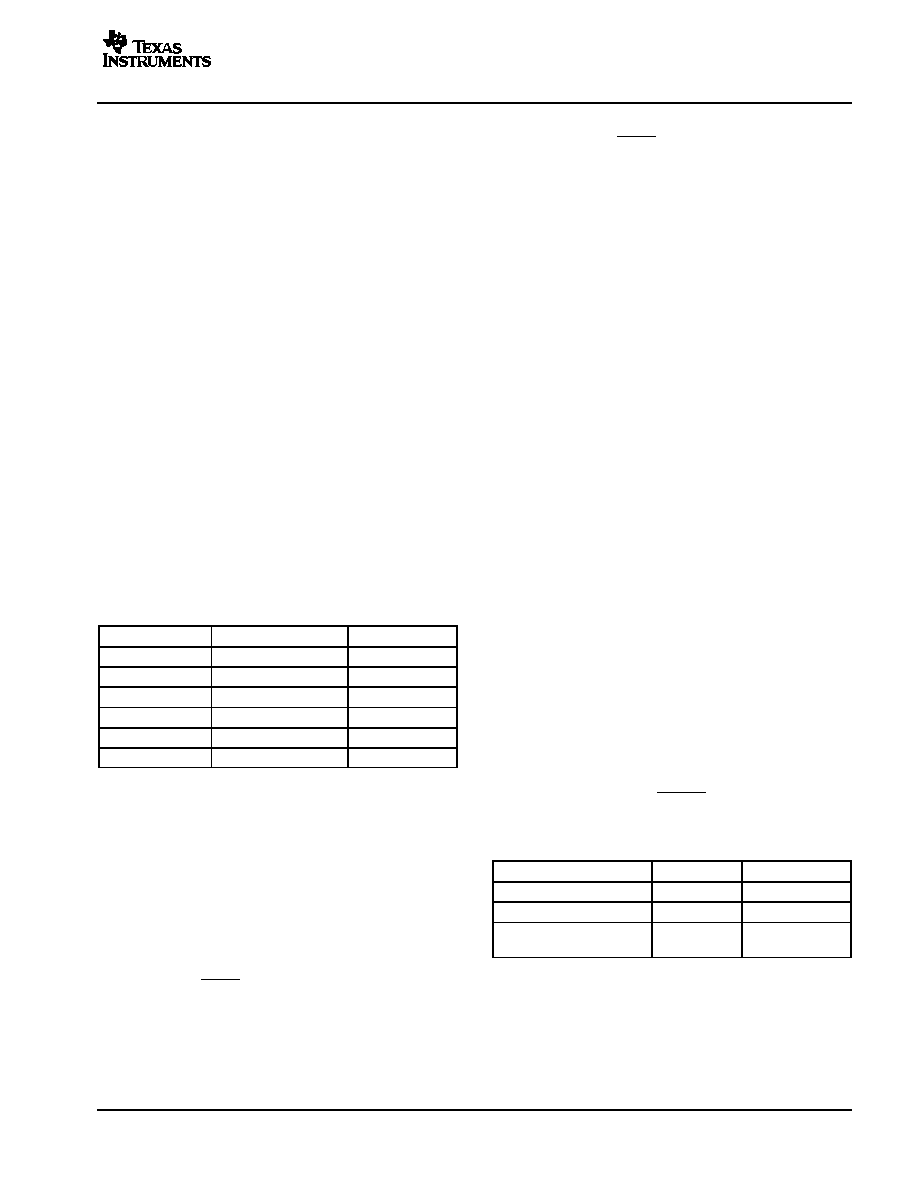

triggering the enable due to noise. Refer to the following

table for start up times for each device

DEVICE

OUTPUT VOLTAGE

SLOW-START

TPS54611

0.9 V

3.3 ms

TPS54612

1.2 V

4.5 ms

TPS54613

1.5 V

5.6 ms

TPS54614

1.8 V

3.3 ms

TPS54615

2.5 V

4.7 ms

TPS54616

3.3 V

6.1 ms

The second function of the SS/ENA pin provides an

external means for extending the slow-start time with a

ceramic capacitor connected between SS/ENA and

AGND. Adding a capacitor to the SS/ENA pin has two

effects on start-up. First, a delay occurs between release

of the SS/ENA pin and start-up of the output. The delay is

proportional to the slow-start capacitor value and lasts until

the SS/ENA pin reaches the enable threshold. The

start-up delay is approximately:

td + C(SS)

1.2 V

5 mA

Second, as the output becomes active, a brief ramp up at

the internal slow-start rate may be observed before the

externally set slow-start rate takes control and the output

rises at a rate proportional to the slow-start capacitor. The

slow-start time set by the capacitor is approximately:

t(SS) + C(SS)

0.7 V

5 mA

The actual slow-start time is likely to be less than the above

approximation due to the brief ramp up at the internal rate.

VBIAS Regulator

The VBIAS regulator provides internal analog and digital

blocks with a stable supply voltage over variations in

junction temperature and input voltage. A high quality,

low-ESR, ceramic bypass capacitor is required on the

VBIAS pin. X7R or X5R grade dielectrics are

recommended because their values are more stable over

temperature. The bypass capacitor should be placed close

to the VBIAS pin and returned to AGND.

External loading on VBIAS is allowed, with the caution that

internal circuits require a minimum VBIAS of 2.7 V, and

external loads on VBIAS with ac or digital switching noise

may degrade performance. The VBIAS pin may be useful

as a reference voltage for external circuits.

Voltage Reference

The voltage reference system produces a precise,

temperature-stable voltage from a bandgap circuit. A

scaling amplifier and DAC are then used to produce the

reference voltages for each of the fixed output devices.

Oscillator and PWM Ramp

The oscillator frequency can be set to internally fixed

values of 350 kHz or 550 kHz using the FSEL pin as a static

digital input. If a different frequency of operation is required

for the application, the oscillator frequency can be

externally adjusted from 280 kHz to 700 kHz by connecting

a resistor from the RT pin to AGND and floating the FSEL

pin. The switching frequency is approximated by the

following equation, where R is the resistance from RT to

AGND:

Switching Frequency + 100 kW

R

500 [kHz]

The following table summarizes the frequency selection

configurations:

SWITCHING FREQUENCY

SYNC PIN

RT PIN

350 kHz, internally set

Float or AGND Float

550 kHz, internally set

≥2.5 V

Float

Externally set 280 kHz to

700 kHz

Float

R = 180 k to 68 k

Error Amplifier

The high performance, wide bandwidth, voltage error

amplifier is gain-limited to provide internal compensation

of the control loop. The user is given limited flexibility in

choosing output L and C filter components. Inductance

values of 4.7 H to 10 H are typical and available from

several vendors. The resulting designs exhibit good noise

(2)

(3)

(4)

相关PDF资料 |

PDF描述 |

|---|---|

| TPS54612PWPRG4 | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| TPS54615PWPR | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| TPS54612PWPR | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| TPS54616PWP | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

| TPS54614PWPG4 | 12 A SWITCHING REGULATOR, 762 kHz SWITCHING FREQ-MAX, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS54615-Q1 | 制造商:TI 制造商全称:Texas Instruments 功能描述:3-V TO 6-V INPUT, 6-A OUTPUT SYNCHRONOUS BUCK PWM SWITCHER WITH INTEGRATED FETs(SWIFT) |

| TPS54615QPWPRQ1 | 功能描述:直流/直流开关调节器 3V-6Vin 6A Out Synch Buck PWM Switcher RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| TPS54616 | 制造商:TI 制造商全称:Texas Instruments 功能描述:3-V TO 6-V INPUT, 6-A OUTPUT SYNCHRONOUS BUCK PWM SWITCHER WITH INTEGRATED FETs |

| TPS54616MPWPREP | 制造商:Texas Instruments 功能描述:CONV DC-DC SINGLE-OUT STEP DOWN 28-PIN TSSOP T/R - Tape and Reel |

| TPS54616PWP | 功能描述:直流/直流开关调节器 Lo-In Vltg 6A Sync Sync Buck Converter RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

发布紧急采购,3分钟左右您将得到回复。