- 您现在的位置:买卖IC网 > PDF目录365968 > TSC21020F-20MA IC CYCLONE III FPGA 16K 256FBGA PDF资料下载

参数资料

| 型号: | TSC21020F-20MA |

| 英文描述: | IC CYCLONE III FPGA 16K 256FBGA |

| 中文描述: | 32位数字信号处理器 |

| 文件页数: | 31/51页 |

| 文件大小: | 763K |

| 代理商: | TSC21020F-20MA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页

31

TSC21020F

4153F

–

AERO

–

06/03

Clock Signal

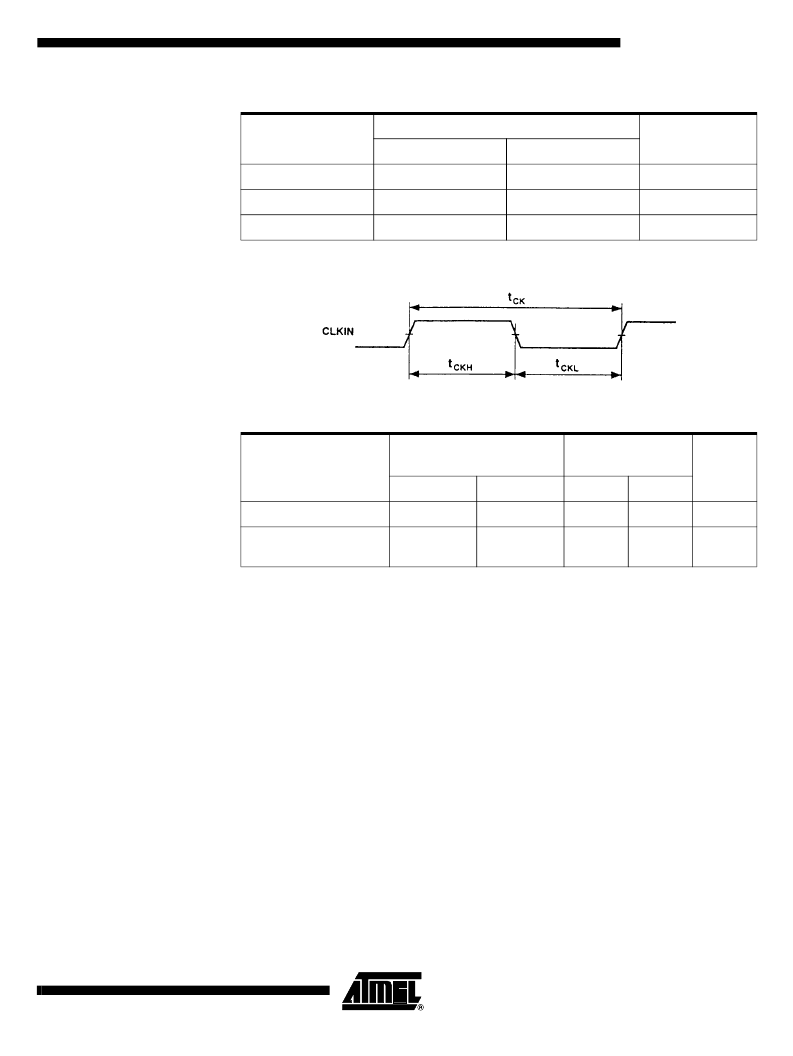

Figure 3.

Clock

Reset

Parameter

20 MHz

Unit

Min

Max

T

CK

CLKIN Period

50

150

ns

t

CKH

CLKIN Width High

10

ns

t

CKL

CLKIN Width Low

10

ns

Parameter

20 MHz

Frequency

Dependency

(1)

Unit

Min

Max

Min

Max

t

WRST

(2)

RESET Width Low

200

4t

CK

ns

t

SRST

before CLKIN High

(3)

RESET Setup

29

50

29 + DT/2

30

ns

Notes:

1. DT = t

CK

- 50 ns

2. Applies after the power-up sequence is complete. At power up, the Internal Phase

Locked Loop requires no more than 1000CLKIN cycles while RESET is low, assum-

ing stable V

DD

and CLKIN (not including clock oscillator start-up time).

3. Specification only applies in cases where multiple TSC21020F processors are

required to execute in program counter lock-step (all processors start execution at

location 8 in the same cycle). See the Hardware Configuration chapter of the

ADSP-21020 User’s Manual from Analog Devices

for reset sequence information.

相关PDF资料 |

PDF描述 |

|---|---|

| TSC21020F-20MBSL3 | IC CYCLONE III FPGA 25K 324 FBGA |

| TSC21020F-20MC-E | FPGA, CYCLONE III, 25K LE, 256UBGA Programmable Logic Type:FPGA; Logic IC function:FPGA; Logic IC family:Cyclone III; Logic IC Base Number:3; I/O lines, No. of:156; |

| TSC21020F-20SA | IC CYCLONE III FPGA 25K 256 UBGA |

| TSC21020F-20SA-E | IC CYCLONE III FPGA 40K 324FBGA |

| TSC21020F-20SAP833 | FPGA, CYCLONE III, 40K LE, 324FBGA Programmable Logic Type:FPGA; Logic IC function:FPGA; Logic IC family:Cyclone III; Logic IC Base Number:3; I/O lines, No. of:195; |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSC21020F-20MA/883 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP|32-BIT|CMOS| RAD HARD|PGA|223PIN|CERAMIC |

| TSC21020F-20MA-E | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Rad. Hard 32/40-bit IEEE Floating Point DSP |

| TSC21020F-20MAP833 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP|32-BIT|CMOS| RAD HARD|PGA|223PIN|CERAMIC |

| TSC21020F-20MASB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP|32-BIT|CMOS| RAD HARD|PGA|223PIN|CERAMIC |

| TSC21020F-20MASC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP|32-BIT|CMOS| RAD HARD|PGA|223PIN|CERAMIC |

发布紧急采购,3分钟左右您将得到回复。