- 您现在的位置:买卖IC网 > PDF目录272328 > TSC80C31-16KAD (ATMEL CORP) 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 PDF资料下载

参数资料

| 型号: | TSC80C31-16KAD |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PDIP40 |

| 封装: | PLASTIC, DIP-40 |

| 文件页数: | 22/83页 |

| 文件大小: | 8336K |

| 代理商: | TSC80C31-16KAD |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

20

8021G–AVR–03/11

ATmega329P/3290P

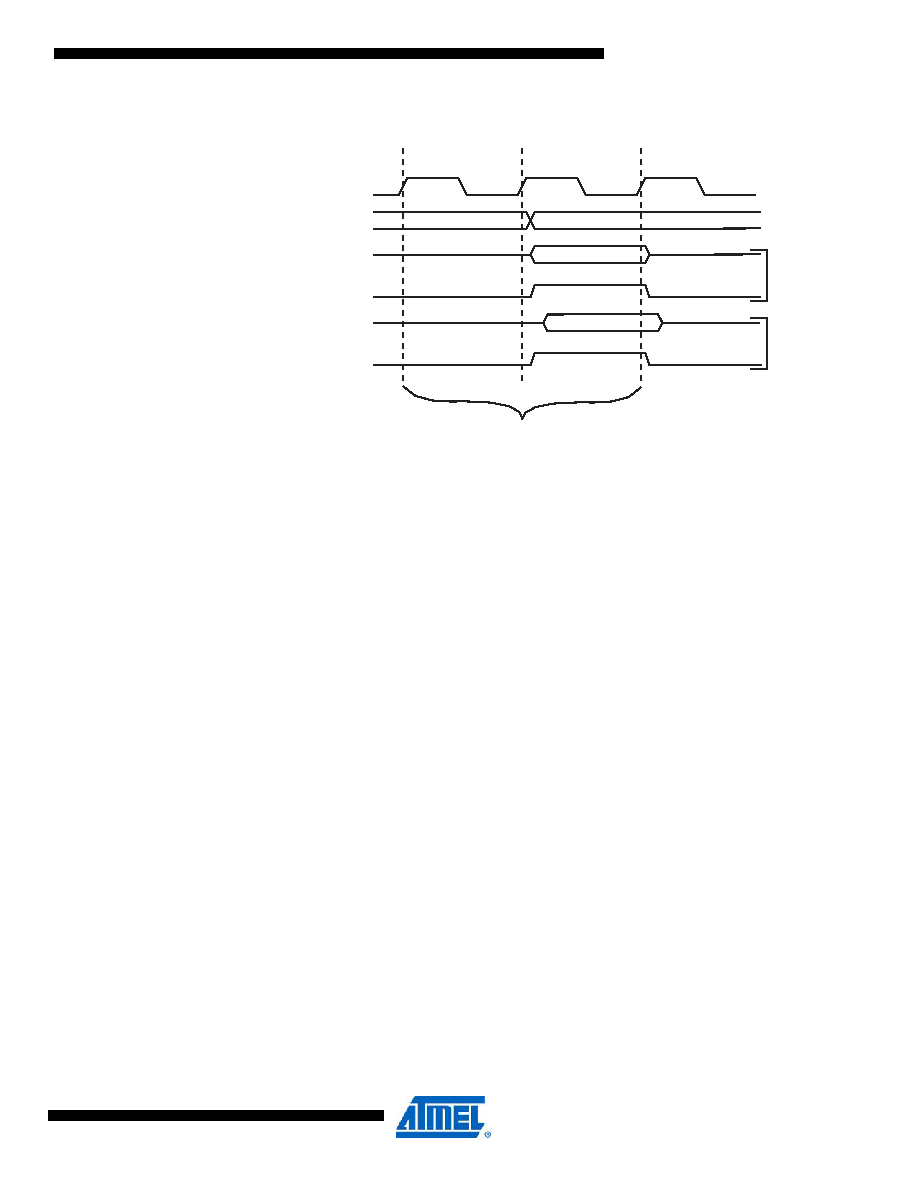

Figure 7-3.

On-chip Data SRAM Access Cycles

7.4

EEPROM Data Memory

The ATmega329P/3290P contains 1Kbytes of data EEPROM memory. It is organized as a sep-

arate data space, in which single bytes can be read and written. The EEPROM has an

endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the

CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM

Data Register, and the EEPROM Control Register.

For a detailed description of SPI, JTAG and Parallel data downloading to the EEPROM, see

7.4.1

EEPROM Write During Power-down Sleep Mode

When entering Power-down sleep mode while an EEPROM write operation is active, the

EEPROM write operation will continue, and will complete before the Write Access time has

passed. However, when the write operation is completed, the clock continues running, and as a

consequence, the device does not enter Power-down entirely. It is therefore recommended to

verify that the EEPROM write operation is completed before entering Power-down.

7.4.2

Preventing EEPROM Corruption

During periods of low V

CC, the EEPROM data can be corrupted because the supply voltage is

too low for the CPU and the EEPROM to operate properly. These issues are the same as for

board level systems using EEPROM, and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First,

a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Sec-

ondly, the CPU itself can execute instructions incorrectly, if the supply voltage is too low.

EEPROM data corruption can easily be avoided by following this design recommendation:

Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can

be done by enabling the internal Brown-out Detector (BOD). If the detection level of the internal

BOD does not match the needed detection level, an external low V

CC reset Protection circuit can

clk

WR

RD

Data

Address

Address valid

T1

T2

T3

Compute Address

Read

Wr

ite

CPU

Memory Access Instruction

Next Instruction

相关PDF资料 |

PDF描述 |

|---|---|

| TSC80C31-40JDB | 8-BIT, 40 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-12LFR | 8-BIT, 12 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-20LFD | 8-BIT, 20 MHz, MICROCONTROLLER, PQFP44 |

| TSC80C31-36KB | 8-BIT, 36 MHz, MICROCONTROLLER, PQCC44 |

| TS87C51RD2-VLMR | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSC80C31-16MA | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

| TSC80C31-16MAB/883 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

| TSC80C31-16MAD/883 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

| TSC80C31-16MAR/883 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

| TSC80C31-16MAR/P883 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 44 MHz Single-Chip 8 Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。