- 您现在的位置:买卖IC网 > PDF目录1971 > UPD70F3714GC-8BS-A (Renesas Electronics America)MCU 32BIT V850ES/LX2 64-LQFP PDF资料下载

参数资料

| 型号: | UPD70F3714GC-8BS-A |

| 厂商: | Renesas Electronics America |

| 文件页数: | 85/320页 |

| 文件大小: | 0K |

| 描述: | MCU 32BIT V850ES/LX2 64-LQFP |

| 标准包装: | 300 |

| 系列: | V850ES/Ix2 |

| 核心处理器: | V850ES |

| 芯体尺寸: | 32-位 |

| 速度: | 20MHz |

| 连通性: | CSI,UART/USART |

| 外围设备: | LVD,PWM,WDT |

| 输入/输出数: | 39 |

| 程序存储器容量: | 128KB(128K x 8) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 6K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 3.5 V ~ 5.5 V |

| 数据转换器: | A/D 8x10b |

| 振荡器型: | 外部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 64-LQFP |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页当前第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页第251页第252页第253页第254页第255页第256页第257页第258页第259页第260页第261页第262页第263页第264页第265页第266页第267页第268页第269页第270页第271页第272页第273页第274页第275页第276页第277页第278页第279页第280页第281页第282页第283页第284页第285页第286页第287页第288页第289页第290页第291页第292页第293页第294页第295页第296页第297页第298页第299页第300页第301页第302页第303页第304页第305页第306页第307页第308页第309页第310页第311页第312页第313页第314页第315页第316页第317页第318页第319页第320页

2011-2012 Microchip Technology Inc.

Preliminary

DS61168D-page 175

PIC32MX1XX/2XX

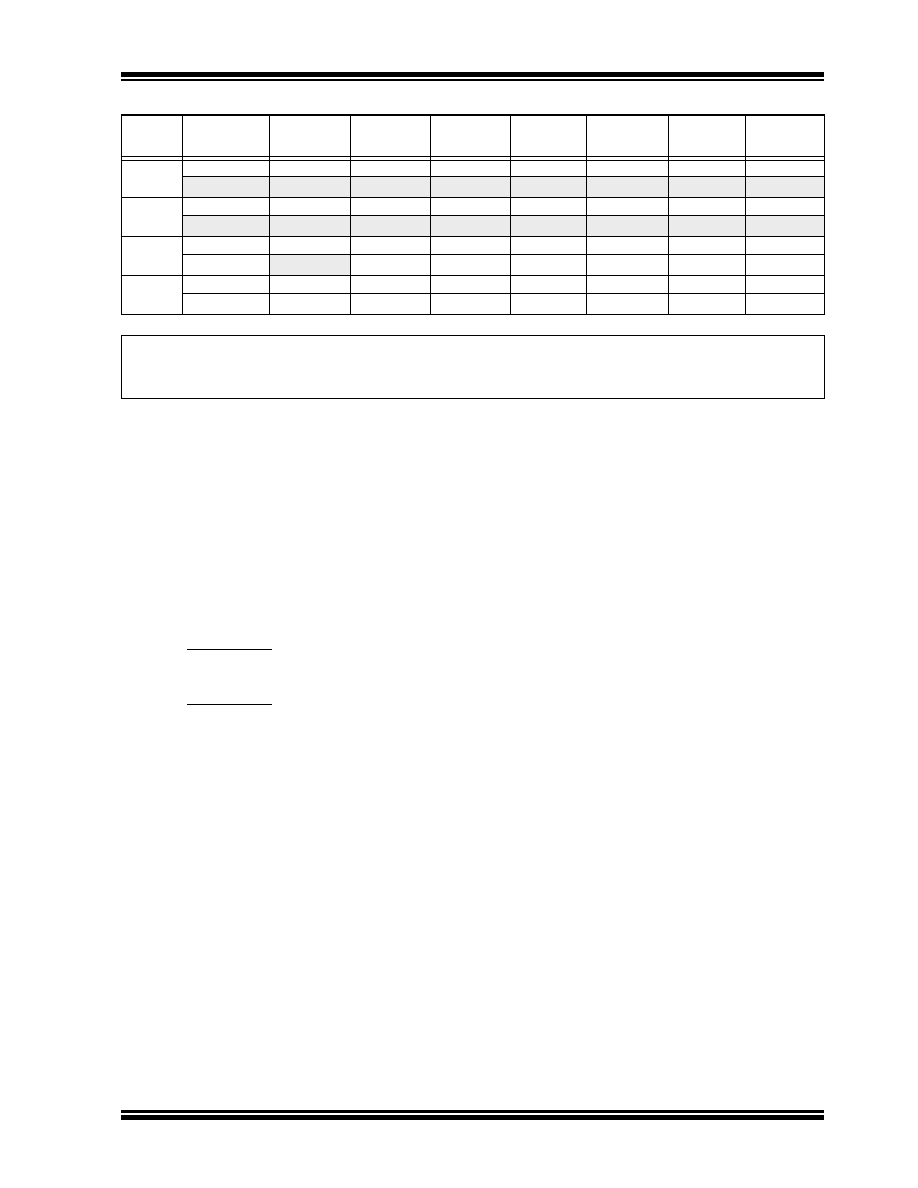

REGISTER 17-1:

I2CXCON: I2C CONTROL REGISTER

Bit

Range

Bit

31/23/15/7

Bit

30/22/14/6

Bit

29/21/13/5

Bit

28/20/12/4

Bit

27/19/11/3

Bit

26/18/10/2

Bit

25/17/9/1

Bit

24/16/8/0

31:24

U-0

—

23:16

U-0

—

15:8

R/W-0

U-0

R/W-0

R/W-1, HC

R/W-0

ON(1)

—

SIDL

SCLREL

STRICT

A10M

DISSLW

SMEN

7:0

R/W-0

R/W-0, HC

GCEN

STREN

ACKDT

ACKEN

RCEN

PEN

RSEN

SEN

Legend:

HC = Cleared in Hardware

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 31-16 Unimplemented: Read as ‘0’

bit 15

ON: I2C Enable bit(1)

1 = Enables the I2C module and configures the SDA and SCL pins as serial port pins

0 = Disables the I2C module; all I2C pins are controlled by PORT functions

bit 14

Unimplemented: Read as ‘0’

bit 13

SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12

SCLREL: SCLx Release Control bit (when operating as I2C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (i.e., software can write ‘0’ to initiate stretch and write ‘1’ to release clock). Hardware clear at

beginning of slave transmission. Hardware clear at end of slave reception.

If STREN = 0:

Bit is R/S (i.e., software can only write ‘1’ to release clock). Hardware clear at beginning of slave

transmission.

bit 11

STRICT: Strict I2C Reserved Address Rule Enable bit

1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate

addresses in reserved address space.

0 = Strict I2C Reserved Address Rule not enabled

bit 10

A10M: 10-bit Slave Address bit

1 = I2CxADD is a 10-bit slave address

0 = I2CxADD is a 7-bit slave address

bit 9

DISSLW: Disable Slew Rate Control bit

1 = Slew rate control disabled

0 = Slew rate control enabled

bit 8

SMEN: SMBus Input Levels bit

1 = Enable I/O pin thresholds compliant with SMBus specification

0 = Disable SMBus input thresholds

Note 1: When using 1:1 PBCLK divisor, the user’s software should not read/write the peripheral’s SFRs in the

SYSCLK cycle immediately following the instruction that clears the module’s ON bit.

相关PDF资料 |

PDF描述 |

|---|---|

| UPD70F3757GJ-GAE-AX | MCU 32BIT V850ES/HX3 144-LQFP |

| UPD720101GJ-UEN-A | HOST CTLR USB 2.0 144-LQFP |

| UPD720102F1-CA7-A | IC HOST CTLR USB2.0 3-PORT BGA |

| UPD720113GK-9EU-A | IC HUB CTLR USB2.0 7-PORTS QFP |

| UPD78F0394GC-8EA-A | MCU 8BIT 48KB FLASH |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPD70F3715GC-8EU-A | 制造商:NEC Electronics Corporation 功能描述:32BIT MCU 128K FLASH 12K RAM SMD |

| UPD70F3716GC-8EA-A | 制造商:NEC Electronics Corporation 功能描述:32BIT MCU 256K FLASH 24K RAM SMD |

| UPD70F3717GC-8EA-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD70F3718GC-8EA-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD70F3719GC(S)-8EA-A | 制造商:NEC Electronics Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。