- 您现在的位置:买卖IC网 > PDF目录361590 > UPSD3234AV-40U6T (意法半导体) Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM PDF资料下载

参数资料

| 型号: | UPSD3234AV-40U6T |

| 厂商: | 意法半导体 |

| 英文描述: | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| 中文描述: | 闪存可编程系统设备与8032微控制器核心和64Kbit SRAM的 |

| 文件页数: | 28/176页 |

| 文件大小: | 1081K |

| 代理商: | UPSD3234AV-40U6T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页

μ

PSD323X

28/176

Jump Instructions

Table 13 shows the list of unconditional jump in-

structions. The table lists a single “JMP add” in-

struction, but in fact there are three SJMP, LJMP,

and AJMP, which differ in the format of the desti-

nation address.JMP is a generic mnemonic which

can be used if the programmer does not care

which way the jump is en-coded.

The SJMP instruction encodes thedestination ad-

dress as a relative offset, as described above. The

instruction is 2 bytes long, consisting of the op-

code and the relative offset byte. The jump dis-

tance is limited to a range of -128 to +127 bytes

relative to the instruction following the SJMP.

The LJMP instruction encodes the destination ad-

dress as a 16-bit constant. The instruction is 3

bytes long, consisting of the opcode and two ad-

dress bytes. The destination address can be any-

where in the 64K Program Memory space.

The AJMP instruction encodes thedestination ad-

dress as an 11-bit constant. The instruction is 2

bytes long, consisting of the opcode, which itself

contains 3 of the 11 address bits, followed by an-

other byte containing the low 8 bits of the destina-

tion address. When the instruction is executed,

these 11 bits are simply substituted for the low 11

bits in the PC. The high 5 bits stay the same.

Hence the destination has to be within the same

2K block as the instruction following the AJMP.

In all cases the programmer specifies the destina-

tion address to the assembler in thesame way: as

a label or as a 16-bit constant. The assembler will

put the destination address into the correct format

for the given instruction. If the format required by

the instruction will not support the distance to the

specified destination address, a “Destination out

of range” message is written into the List file.

The JMP @A+DPTR instruction supports case

jumps. The destination address is computed atex-

ecution time as the sum of the 16-bit DPTR regis-

ter and the Accumulator. Typically. DPTR is set up

with the address of a jump table. In a 5-way

branch, for ex-ample, an integer 0 through 4 is

loaded into the Accumulator. The code to be exe-

cuted might be as follows:

MOV DPTR,#JUMP TABLE

MOV A,INDEX_NUMBER

RL A

JMP @A+DPTR

The RL Ainstruction converts the index number (0

through 4) to an even number on the range 0

through 8, because each entry in the jump table is

2 bytes long:

JUMP TABLE:

AJMP CASE 0

AJMP CASE 1

AJMP CASE 2

AJMP CASE 3

AJMP CASE 4

Table 13 shows a single “CALL addr” instruction,

but there are two of them, LCALL and ACALL,

which differ in the format in which the subroutine

address is given to the CPU. CALL is a generic

mnemonic which can be used if the programmer

does not care which way the address is encoded.

The LCALL instruction uses the16-bit address for-

mat, and the subroutine can be anywhere in the

64K Program Memory space. The ACALL instruc-

tion uses the 11-bit format, and the subroutine

must be inthe same 2K block as the instructionfol-

lowing the ACALL.

In any case, the programmer specifies the subrou-

tine address to the assembler in thesame way: as

a label or as a 16-bit constant. The assembler will

put the address into the correct format for the giv-

en instructions.

Subroutines should end with a RET instruction,

which returns execution to the instruction following

the CALL.

RETI is used to return from an interrupt service

routine. The only difference between RET and

RETI is that RETI tellsthe interrupt control system

that the interrupt in progress is done. If there is no

interrupt in progress at the time RETI is executed,

then the RETI is functionally identical to RET.

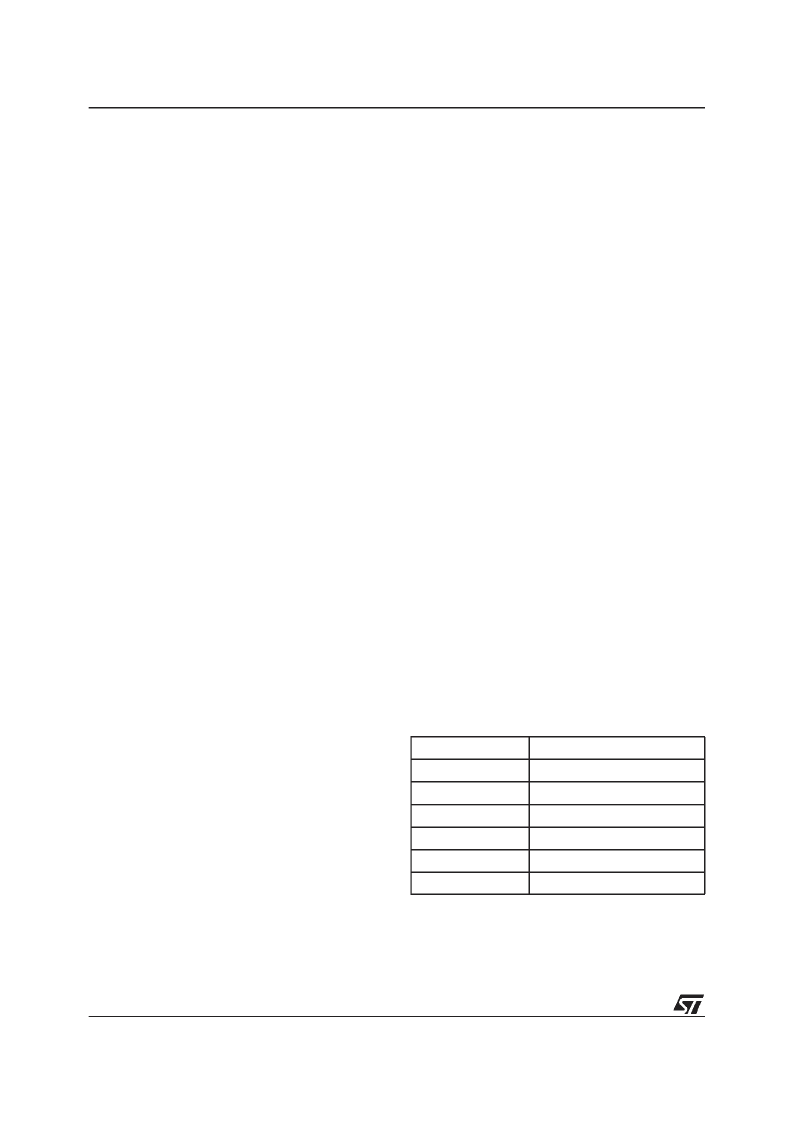

Table 13. Unconditional Jump Instructions

Mnemonic

Operation

JMP addr

Jump to addr

JMP @A+DPTR

Jump to A+DPTR

CALL addr

Call Subroutine at addr

RET

Return from subroutine

RETI

Return from interrupt

NOP

No operation

相关PDF资料 |

PDF描述 |

|---|---|

| UPSD3213B-24U1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40T1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40T6T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213B-40U1T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

| UPSD3213BV-40U6T | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPSD3234B-24T1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3234B-24T1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Devices with 8032 Microcontroller Core |

| UPSD3234B-24T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

| UPSD3234B-24T6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Devices with 8032 Microcontroller Core |

| UPSD3234B-24U1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash Programmable System Device with 8032 Microcontroller Core |

发布紧急采购,3分钟左右您将得到回复。