- 您现在的位置:买卖IC网 > PDF目录225499 > V54C3128164VBLJ-7IPC (PROMOS TECHNOLOGIES INC) SYNCHRONOUS DRAM, PBGA60 PDF资料下载

参数资料

| 型号: | V54C3128164VBLJ-7IPC |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | SYNCHRONOUS DRAM, PBGA60 |

| 封装: | GREEN, MO-210, FBGA-60 |

| 文件页数: | 1/56页 |

| 文件大小: | 725K |

| 代理商: | V54C3128164VBLJ-7IPC |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

1

V54C3128(16/80/40)4VB*I

128Mbit SDRAM, INDUSTRIAL TEMPERATURE

3.3 VOLT, TSOP II / FBGA

8M X 16, 16M X 8, 32M X 4

V54C3128(16/80/40)4VB*I Rev. 1.5 June 2008

67PC

7

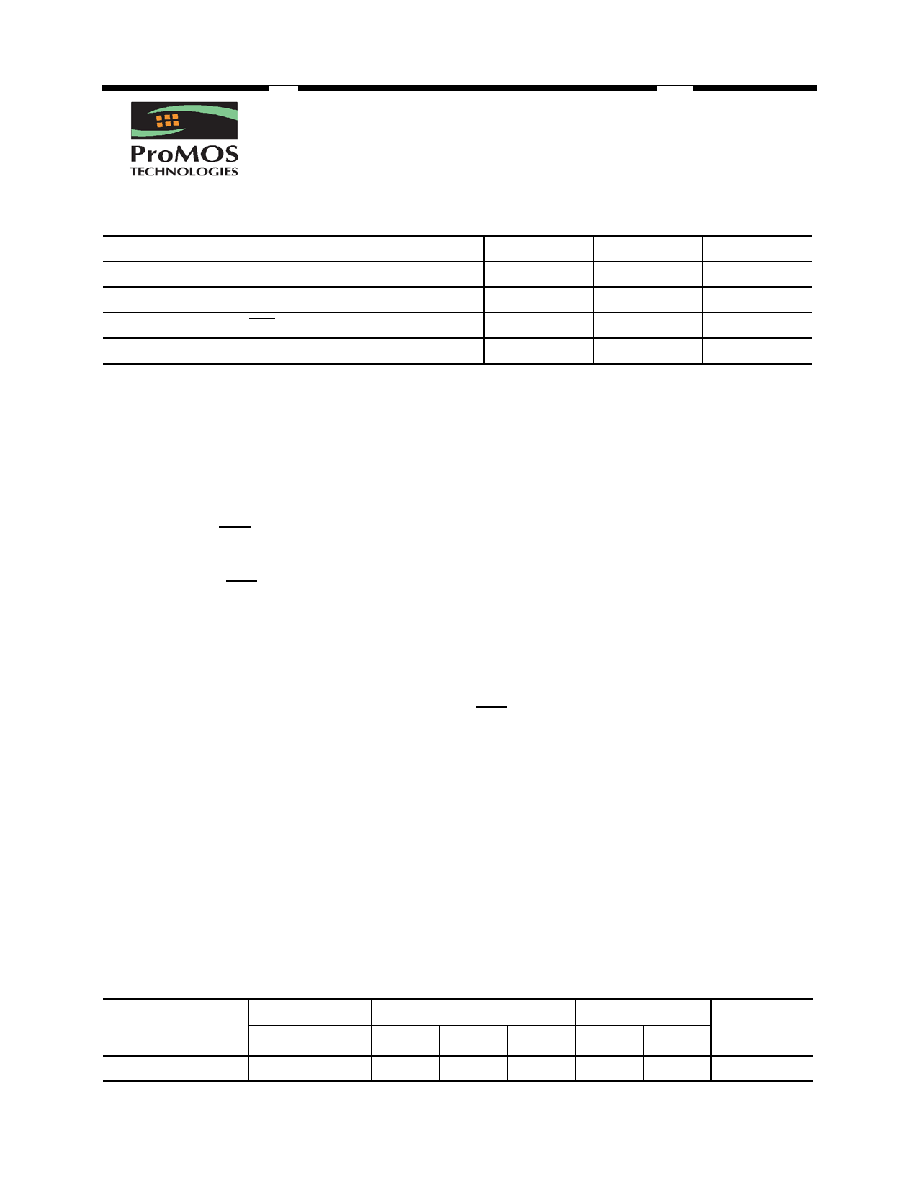

System Frequency (fCK)

166 MHz

143 MHz

Clock Cycle Time (tCK3)

6 ns

7 ns

Clock Access Time (tAC3) CAS Latency = 3

5.4 ns

Clock Access Time (tAC2) CAS Latency = 2

5.4 ns

6 ns

Features

■ 4 banks x 2Mbit x 16 organization

■ 4 banks x 4Mbit x 8 organization

■ 4 banks x 8Mbit x 4 organization

■ High speed data transfer rates up to 166 MHz

■ Full Synchronous Dynamic RAM, with all signals

referenced to clock rising edge

■ Single Pulsed RAS Interface

■ Data Mask for Read/Write Control

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS Latency: 2, 3

■ Programmable Wrap Sequence: Sequential or

Interleave

■ Programmable Burst Length:

1, 2, 4, 8, and full page for Sequential Type

1, 2, 4, 8 for Interleave Type

■ Multiple Burst Read with Single Write Operation

■ Automatic and Controlled Precharge Command

■ Random Column Address every CLK (1-N Rule)

■ Power Down Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval: 4096 cycles/64 ms

■ Available in 54-ball FBGA, 60-ball FBGA and

54-Pin TSOPII

■ LVTTL Interface

■ Single (+3.0 V ~3.3V)

±0.3 V Power Supply

■ Industrial Temperature (TA): -40C to +85C

Description

The V54C3128(16/80/40)4VB*I is a four bank

Synchronous DRAM organized as 4 banks x 2Mbit

x 16, 4 banks x 4Mbit x 8, or 4 banks x 8Mbit x 4.

The

V54C3128(16/80/40)4VB*I

achieves

high

speed data transfer rates up to 166 MHz by employ-

ing a chip architecture that prefetches multiple bits

and then synchronizes the output data to a system

clock.

All of the control, address, data input and output

circuits are synchronized with the positive edge of

an externally supplied clock.

Operating the four memory banks in an inter-

leaved fashion allows random access operation to

occur at higher rate than is possible with standard

DRAMs. A sequential and gapless data rate of up to

166 MHz is possible depending on burst length,

CAS latency and speed grade of the device.

Device Usage Chart

Operating

Temperature

Range

Package Outline

Access Time (ns)

Power

Temperature

Mark

C/S/T

6

7PC

7

Std.

L

-40

°C to +85°C

I

相关PDF资料 |

PDF描述 |

|---|---|

| V54C3128404VBLE7PC | 32M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3128404VBLF8PC | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PBGA60 |

| V54C365804VCT8L | 8M X 8 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| V55C2256164VGLK-10H | SYNCHRONOUS DRAM, PBGA54 |

| V585ME07 | VCO, 1100 MHz - 2100 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V54C3128164VS | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128164VT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128404VBGA | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, BGA PACKAGE |

| V54C3128404VS | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128404VT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

发布紧急采购,3分钟左右您将得到回复。