- 您现在的位置:买卖IC网 > PDF目录202172 > V54C3256404VDLJ6 (PROMOS TECHNOLOGIES INC) 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 PDF资料下载

参数资料

| 型号: | V54C3256404VDLJ6 |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 |

| 封装: | GREEN, MO-210, FBGA-60 |

| 文件页数: | 11/56页 |

| 文件大小: | 719K |

| 代理商: | V54C3256404VDLJ6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

19

V54C3256(16/80/40)4VD Rev. 1.9 August 2008

ProMOS TECHNOLOGIES

V54C3256(16/80/40)4VD

Notes for AC Parameters:

1.

For proper power-up see the operation section of this data sheet.

2.

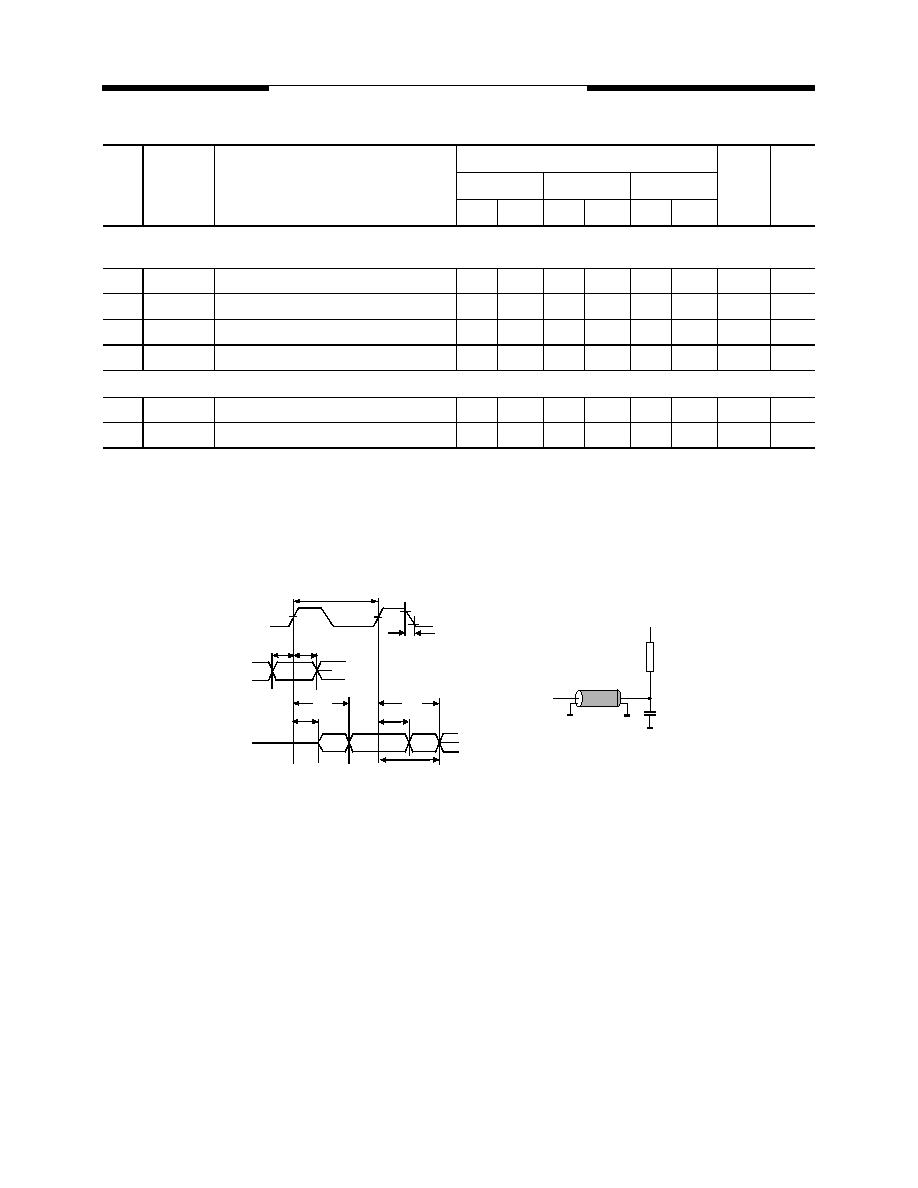

AC timing tests have VIL = 0.8V and VIH = 2.0V with the timing referenced to the 1.4 V crossover point. The transition

time is measured between VIH and VIL. All AC measurements assume tT = 1ns with the AC output load circuit shown

in Figure 1.

4.

If clock rising time is longer than 1 ns, a time (tT/2 – 0.5) ns has to be added to this parameter.

5.

If tT is longer than 1 ns, a time (tT – 1) ns has to be added to this parameter.

6.

These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as

follows:

the number of clock cycle = specified value of timing period (counted in fractions as a whole number)

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.

Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command

is registered.

7.

Referenced to the time which the output achieves the open circuit condition, not to output voltage levels

Read Cycle

24

tOH

Data Out Hold Time

2.5

–

3

–

3

–

ns

2

25

tLZ

Data Out to Low Impedance Time

1

–

1

–

1

–

ns

26

tHZ

Data Out to High Impedance Time

3

6

3

7

3

7

ns

7

27

tDQZ

DQM Data Out Disable Latency

–

2

–

2

–

2

CLK

Write Cycle

28

tWR

Write Recovery Time for Auto precharge

2

–

2

–

2

–

CLK

29

tDQW

DQM Write Mask Latency

0

–

0

–

0

–

CLK

#

Symbol

Parameter

Limit Values

Unit

Note

-6

-7PC

-7

Min.

Max.

Min.

Max.

Min.

Max.

1.4V

tIS

tIH

tAC

tLZ

tOH

tHZ

CLK

COMMAND

OUTPUT

50 pF

I/O

Z=50 Ohm

+ 1.4 V

50 Ohm

VIH

VIL

tT

Figure 1.

tCK

相关PDF资料 |

PDF描述 |

|---|---|

| V54C3256404VDUI6 | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3256404VDUS7 | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 |

| V54C3256404VHLI6I | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3256404VHUI6I | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3256804VBS7 | 32M X 8 SYNCHRONOUS DRAM, 5.4 ns, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V54C3256404VS | 制造商:MOSEL 制造商全称:MOSEL 功能描述:256Mbit SDRAM 3.3 VOLT, TSOP II / SOC BGA / WBGA PACKAGE 16M X 16, 32M X 8, 64M X 4 |

| V54C3256404VT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:256Mbit SDRAM 3.3 VOLT, TSOP II / SOC BGA / WBGA PACKAGE 16M X 16, 32M X 8, 64M X 4 |

| V54C3256804VAB | 制造商:MOSEL 制造商全称:MOSEL 功能描述:256Mbit SDRAM 3.3 VOLT, TSOP II / SOC BGA / WBGA PACKAGE 16M X 16, 32M X 8, 64M X 4 |

| V54C3256804VAT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:256Mbit SDRAM 3.3 VOLT, TSOP II / SOC BGA / WBGA PACKAGE 16M X 16, 32M X 8, 64M X 4 |

| V54C3256804VB | 制造商:MOSEL 制造商全称:MOSEL 功能描述:256Mbit SDRAM 3.3 VOLT, TSOP II / SOC BGA / WBGA PACKAGE 16M X 16, 32M X 8, 64M X 4 |

发布紧急采购,3分钟左右您将得到回复。