- 您现在的位置:买卖IC网 > PDF目录16112 > VDSP-SHARC-PC-FULL (Analog Devices Inc)VISUALDSP++ FOR IDE TOOLS SHARC PDF资料下载

参数资料

| 型号: | VDSP-SHARC-PC-FULL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 2/4页 |

| 文件大小: | 0K |

| 描述: | VISUALDSP++ FOR IDE TOOLS SHARC |

| 产品培训模块: | Introduction to VisualDSP++® Tools SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | Visual DSP++? IDDE |

| 适用于相关产品: | SHARC? 处理器 |

| 其它名称: | Q5824280 VDSP-SHARC-PCFULL VDSP-SHARC-PCFULL-ND VDSPU-SHARC-PCFULL |

�� �

�

�

�A� compiler’s� overriding� mission� is� to� produce� correct� code,� so� there�

�are� occasions� when� the� compiler� must� take� a� conservative� approach�

�to� a� code� sequence� when� a� more� aggressive� approach� could� have�

�been� taken� if� certain� constraints� could� be� guaranteed� by� the�

�programmer.� The� VisualDSP++� compiler� supports� a� broad� range� of�

�pragma� that� allow� the� programmer� to� better� exploit� the� compiler�

�while� maintaining� C� language� neutrality.� Just� as� important,� the�

�compiler� has� the� ability� to� feed� back� advisory� information� to� the�

�programmer,� offering� further� improvements� to� a� code� sequence� should�

�the� programmer� be� able� to� make� certain� guarantees� about� it.� This�

�information� is� displayed� seamlessly� in� the� VisualDSP++� main� editor�

�window.� This� “lifts� the� veil”� off� the� “black� box”� that� compilers� are� often,�

�and� accurately,� accused� of� being.�

�Backing� the� compiler� is� a� powerful� assembler� and� linker� technology.�

�Analog� Devices’� processors� are� noted� for� their� intuitive� algebraic�

�assembly� language� syntax,� and� the� VisualDSP++� assembler� extends� that�

�ease� of� use� with� the� ability� to� import� C� header� files,� allowing� for� symbolic�

�references� into� arbitrarily� complex� C� data� structures.� Binary� data� can�

�be� “included”� directly� into� assembly� source� files,� creating� an� easy� way�

�to� add� blocks� of� static� data� (such� as� audio� samples� and� bitmaps)� to� an�

�application.� The� VisualDSP++� linker� is� fully� multicore� and� multiprocessor�

�(MP)� aware,� allowing� for� the� creation� of� cross-linked,� multiexecutable�

�applications� in� a� single� pass.� Other� powerful� capabilities� of� the� linker�

�include� dead� code� and� data� elimination,� code� and� data� overlays,� section�

�spilling� (i.e.,� automatic� overflow� from� internal� to� external� memory),� and�

�automatic� short-to-long� call� expansion.�

�Leverage� Proven� Application� Infrastructure�

�VisualDSP++� goes� beyond� robust� code� generation� tools,� providing�

�considerable� application� infrastructure� and� middleware� out� of� the� box�

�to� speed� application� development.� The� VisualDSP++� kernel� (VDK)� is� a�

�robust,� royalty-free,� real-time� operating� system� (RTOS)� kernel.� It� provides�

�essential� kernel� features� in� a� minimal� footprint.� Features� include� a� fully�

�preemptive� scheduler� (time� slicing� and� cooperative� scheduling� are� also�

�supported),� thread� creation,� semaphores,� interrupt� management,� inter-�

�thread� messaging,� events,� and� memory� management� (memory� pools�

�and� multiple� heaps).� In� MP� environments,� MP� messaging� is� also�

�provided.� Configuration� of� these� elements� is� done� graphically� with� code�

�wizards� to� speed� the� creation� of� new� threads� and� interrupt� handlers.�

�VDK� has� been� available� for� multiple� releases� of� VisualDSP++� and� is� now�

�a� key� component� of� products� shipping� from� a� number� of� high� volume�

�vendors.� Several� commercial� RTOSs� are� also� available� from� select� Analog�

�Devices� third� parties.�

�Blackfin� Processors� can� take� advantage� of� the� system� service� library�

�(SSL),� which� provides� consistent,� easy� C� language� access� to� Blackfin�

�features� such� as� the� interrupt� manager,� direct� memory� access� (DMA),�

�and� power� management� units.� Clock� frequency� and� voltage� can� be�

�changed� easily� at� run� time� through� a� set� of� simple� APIs.� Interrupt�

�handling� can� be� live,� fired� at� the� time� of� the� event,� or� deferred� to� a� later�

�time� of� the� application’s� choosing.� A� device� manager� integrates� device�

�drivers� for� on-� and� off-chip� peripherals.� VisualDSP++� includes� ever�

�expanding� device� driver� support� for� all� on-chip� peripherals� and� off-chip�

�devices� found� on� Analog� Devices� EZ-KIT� Lite� and� EZ-Extender� ?� products.�

�The� SSL� is� OS-neutral� and� can� be� run� as� a� standalone� or� in� conjunction�

�with� an� RTOS.�

�Built� upon� the� system� service� library,� the� file� system� service� (FSS)�

�provides� a� portable� and� extensible� means� of� accessing� mass�

�storage� media� from� the� Blackfin� Processor.� Support� for� the�

�ADSP-BF548� EZ-KIT� Lite� development� board� is� provided� with�

�VisualDSP++� 5.0� for� FAT� file� systems� on� the� attached� hard� disk�

�drive,� supplied� SD� card,� and� USB� flash.�

�As� embedded� applications� become� increasingly� part� of� the� connected�

�world,� the� ability� to� rapidly� add� reliable� Ethernet� or� USB� connectivity�

�to� an� application� can� often� make� or� break� a� development� schedule.�

�For� Blackfin� Processors,� VisualDSP++� includes� a� tuned� port� of� the�

�open� source� LwIP� TCP/IP� stack.� An� example� application� showcasing�

�an� embedded� Web� server� is� among� the� highlights� of� this� support.� For�

�Blackfin� Processors� and� SHARC� Processors,� USB� 2.0� device� connectivity�

�is� provided.� Bulk� and� asynchronous� transfer� modes� are� supported� out�

�of� the� box,� with� USB-IF� logo� certified� embedded� and� host� applications�

�provided� with� full� source� code.�

�Source� code� generation.�

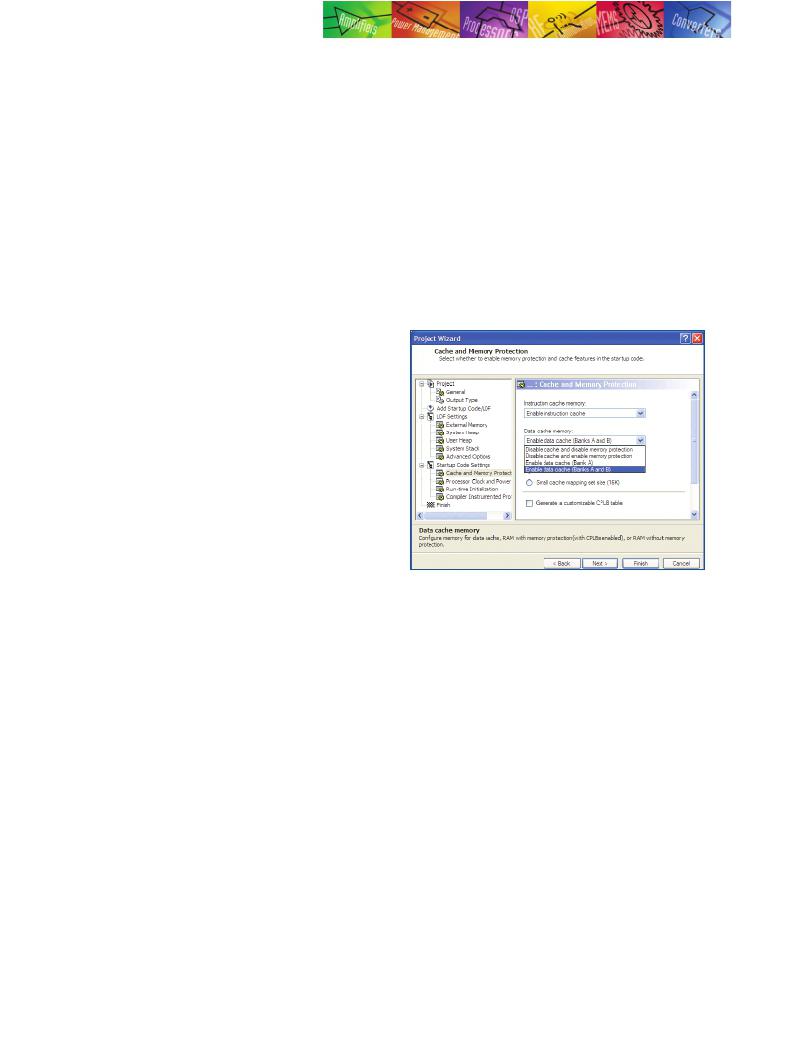

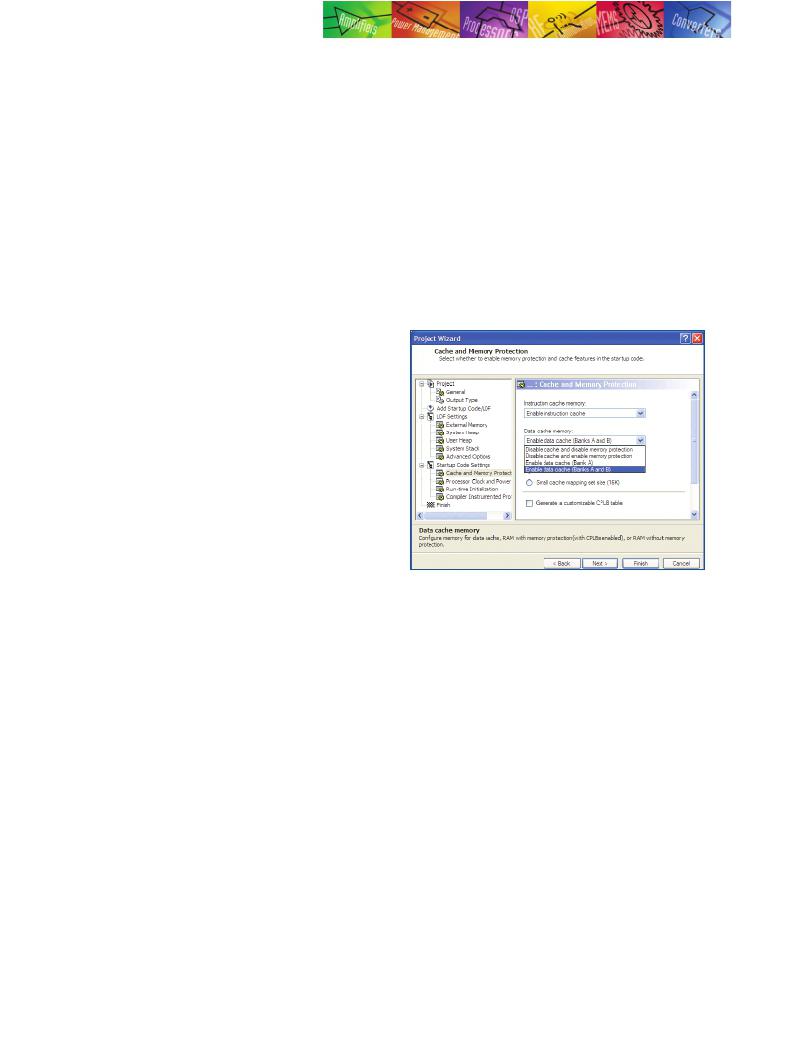

�Wrapping� all� of� these� powerful� tools� and� libraries� together� is� the�

�VisualDSP++� state-of-the-art� integrated� development� and� debugging�

�environment� (IDDE).� The� IDDE� includes� full-featured� editing� and� project�

�manage-ment� tools� with� incremental� builds,� multiple� build� configurations�

�(“Debug”� and� “Release,”� for� example),� syntax-coloring� editor,� and� many�

�other� code� editing� features.� Makefiles� can� be� imported� and� exported�

�freely.� For� Blackfin� Processors,� many� application� attributes� can� be�

�configured� graphically,� enabling� point-and-click� access� to� SDRAM� setup,�

�stack� and� heap� placement,� power� management,� clock� speed,� cache�

�setup,� and� more.�

�Debug� and� Tune� Your� Application� with� Ease�

�The� ability� to� develop� a� high� performance� application� is� often� gated�

�by� the� visibility� into� your� running� system� that� your� debugger� provides.�

�VisualDSP++� excels� in� this� regard,� with� best-in-class� debugging� and�

�inspection� support.� Robust� fundamental� C� language� source� debugging�

�(source-level� stepping� and� breakpoints,� stack� unwinds,� local� variable�

�and� C� expression� support,� memory� and� register� windows)� serves� as� a�

�foundation� upon� which� multiple� innovative� and� unique� tools� rest.�

�VisualDSP++� supports� a� variety� of� debugging� targets.� Most� common� is�

�a� JTAG� connection� to� an� EZ-KIT� Lite� board� or� to� a� custom� target� board�

�by� means� of� Analog� Devices� emulator� products.� However,� there� will� be�

�相关PDF资料 |

PDF描述 |

|---|---|

| M3BBK-4018R | IDC CABLE - MSR40K/MC40M/MSR40K |

| M3CMK-2020K | IDC CABLE - MKC20K/MC20F/MCG20K |

| UWT1V4R7MCL1GB | CAP ALUM 4.7UF 35V 20% SMD |

| M3AMK-2020K | IDC CABLE - MSC20K/MC20F/MCG20K |

| M3YYK-1640K | IDC CABLE - MPD16K/MC16F/MPD16K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| VDSP-TS-PCFLOAT | 功能描述:VISUAL DSP IDE TOOL TIGERSHARC RoHS:是 类别:编程器,开发系统 >> 软件 系列:TigerSHARC® 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| VDSP-TS-PCFLT-5 | 功能描述:SOFTWARE TGRSHARC PC FLOAT 5SEAT RoHS:否 类别:编程器,开发系统 >> 软件 系列:TigerSHARC® 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| VDSP-TS-PC-FULL | 功能描述:VISUAL DSP++ TOOL TIGERSHARC RoHS:否 类别:编程器,开发系统 >> 软件 系列:TigerSHARC® 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| VDSPU_SHARC_PCFULL | 制造商:Analog Devices 功能描述:EMULATOR ((NS)) |

| VDSPU-BLKFNPCFLOAT | 制造商:Analog Devices 功能描述:VISUALDSP++ - Virtual or Non-Physical Inventory (Software & Literature) |

发布紧急采购,3分钟左右您将得到回复。