- 您现在的位置:买卖IC网 > PDF目录16112 > VTERB-BLK-X2-U4 (Lattice Semiconductor Corporation)IP CORE VITERBI DECODER XP2 PDF资料下载

参数资料

| 型号: | VTERB-BLK-X2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 4/34页 |

| 文件大小: | 0K |

| 描述: | IP CORE VITERBI DECODER XP2 |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | VTERBBLKX2U4 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

Chapter� 1:�

�Introduction�

�The� Block� Viterbi� Decoder� IP� core� is� a� parameterizable� Viterbi� Decoder� for� decoding� different� combinations� of� con-�

�volutionally� encoded� sequences.� The� decoder� supports� various� code� rates,� constraint� lengths,� and� generator� poly-�

�nomials.� It� also� allows� soft-decision� decoding� and� is� capable� of� decoding� punctured� codes.� The� core� can� operate� in�

�continuous� or� block� modes,� whichever� is� required� by� the� channel.� Either� Tail� Biting� or� Zero� Flushing� convolutional�

�codes� can� be� decoded� in� the� block� mode.� All� the� configurable� parameters,� including� operation� mode,� generator�

�polynomials,� punctured� block� size,� and� puncture� pattern� can� be� defined� by� the� user� to� suit� the� needs� of� their� appli-�

�cation.� The� code� rate� and� puncture� pattern� can� also� be� changed� dynamically� through� input� ports� during� the� opera-�

�tion� of� the� decoder.� Lattice’s� Block� Viterbi� Decoder� IP� is� compatible� with� many� networking� and� wireless� standards�

�that� use� different� methods� of� convolutional� encoding� at� the� encoder.�

�Quick� Facts�

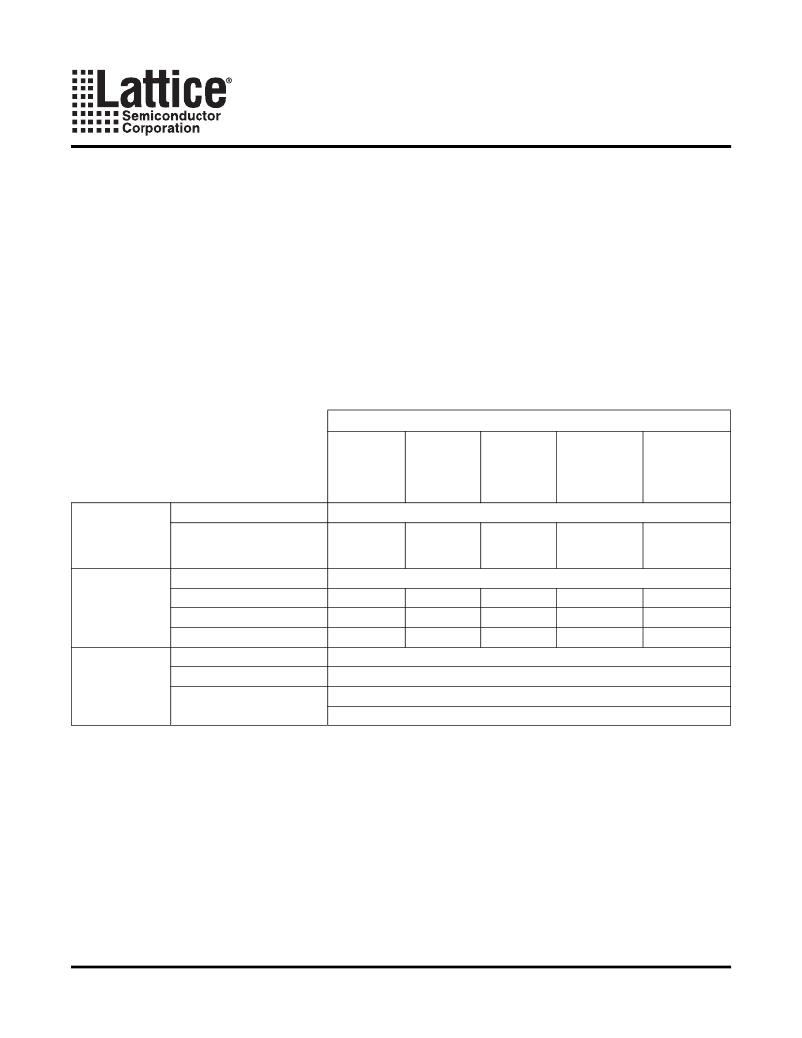

�Table� 1-1� through� Table� 1-4� give� quick� facts� about� the� Block� Viterbi� Decoder� IP� core� for� LatticeEC?,� Lat-�

�ticeECP?,� LatticeECP2?,� LatticeECP2M?,� LatticeECP3?,� LattticeSC?,� LatticeSCM?,� LatticeXP?,� and�

�LatticeXP2?,� devices.�

�Table� 1-1.� Block� Viterbi� Decoder� IP� Core� for� LatticeEC/ECP/XP� Devices� Quick� Facts�

�Block� Viterbi� IP� Configuration�

�IEEE�

�802.16�

�2004-� SC�

�PHY�

�3GPP�

�DVB-S�

�IEEE�

�802.11A�

�IEEE� 802.16-�

�2004-OFDM�

�PHY�

�(dynamic�

�puncturing)�

�IEEE� 802.16-�

�2004-OFDM�

�PHY� (fixed�

�puncturing)�

�FPGA� Families� Supported�

�LatticeEC/ECP/XP�

�Core� ?�

�Requirements�

�Minimal� Device� Needed�

�LFEC1E�

�LFECP6E�

�LFXP3C�

�LFEC10E�

�LFECP10E�

�LFXP10C�

�LFEC3E�

�LFECP6E�

�LFXP3C�

�LFEC3E�

�LFECP6E�

�LFXP3C�

�LFEC6E�

�LFECP6E�

�LFXP6C�

�Targeted� Device�

�LFEC20E-5F672C/� LFECP20E-5F672C/� LFXP20E-5F256C�

�Resource� ?�

�Utilization�

�LUTs�

�sysMEM� EBRs�

�Registers�

�500�

�2�

�250�

�9950�

�16�

�3200�

�2600�

�4�

�900�

�2750�

�4�

�1050�

�3300�

�4�

�1200�

�Lattice� Implementation�

�Diamond� ?� 1.0� or� ispLEVER� ?� 8.1�

�Design� Tool� ?�

�Support�

�Synthesis�

�Simulation�

�Synopsys� ?� Synplify� ?� Pro� for� Lattice� D-2009.12L-1�

�Aldec� ?� Active-HDL� ?� 8.2� Lattice� Edition�

�Mentor� Graphics� ?� ModelSim� ?� SE� 6.3F�

�IPUG32_02.7,� June� 2010�

�4�

�Block� Viterbi� Decoder� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| A3DDH-6418M | IDC CABLE - AKR64H/AE64M/AKR64H |

| M3DFK-3406R | IDC CABLE - MKR34K/MC34M/MCF34K |

| VTERB-BLK-SC-U4 | IP CORE VITERBI DECODER SC/SCM |

| VTERB-BLK-PM-U4 | IP CORE VITERBI DECODER ECPM |

| M3DGK-3406R | IDC CABLE - MKR34K/MC34M/MCS34K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| VTERB-BLK-X2-UT4 | 功能描述:开发软件 VITERBI DECODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| VTERB-BLK-XM-U4 | 功能描述:编码器、解码器、复用器和解复用器 Block Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| VTERB-DECO-O4-N1 | 功能描述:编码器、解码器、复用器和解复用器 Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| VTERB-DECO-XP-N1 | 功能描述:编码器、解码器、复用器和解复用器 Viterbi Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| VTESALLANF-155.520000 | 功能描述:155.52MHz LVPECL VCXO Oscillator Surface Mount 3.3V 100mA Enable/Disable 制造商:taitien 系列:VT 包装:剪带 零件状态:新产品 类型:VCXO 频率:155.52MHz 功能:启用/禁用 输出:LVPECL 电压 - 电源:3.3V 频率稳定度:±50ppm 工作温度:-40°C ~ 85°C 电流 - 电源(最大值):100mA 等级:- 安装类型:表面贴装 大小/尺寸:0.276" 长 x 0.197" 宽(7.00mm x 5.00mm) 高度:0.075"(1.90mm) 封装/外壳:6-SMD,无引线(DFN,LCC) 电流 - 电源(禁用)(最大值):- 标准包装:200 |

发布紧急采购,3分钟左右您将得到回复。