- 您现在的位置:买卖IC网 > PDF目录363887 > W48C111-16 (Cypress Semiconductor Corp.) Frequency Generator for Integrated Core Logic(在集成核心逻辑中应用的频率发生器) PDF资料下载

参数资料

| 型号: | W48C111-16 |

| 厂商: | Cypress Semiconductor Corp. |

| 英文描述: | Frequency Generator for Integrated Core Logic(在集成核心逻辑中应用的频率发生器) |

| 中文描述: | 频率发生器集成的核心逻辑(在集成核心逻辑中应用的频率发生器) |

| 文件页数: | 5/7页 |

| 文件大小: | 114K |

| 代理商: | W48C111-16 |

W48C111-16

PRELIMINARY

5

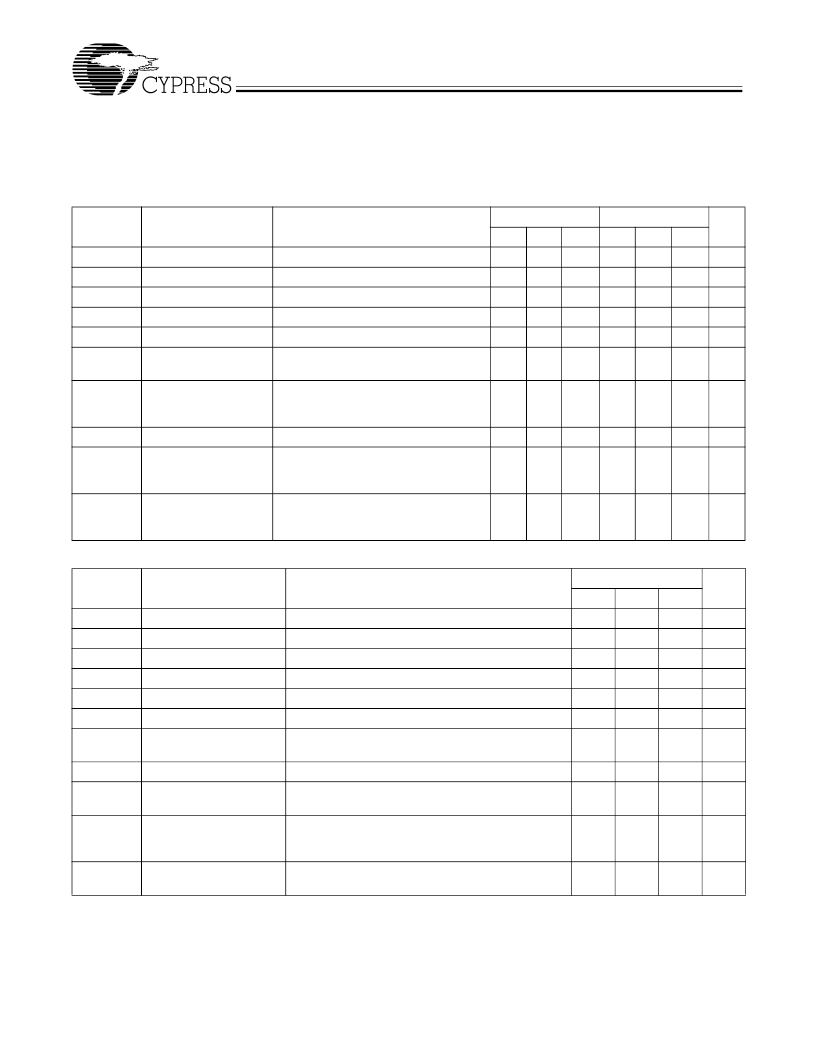

AC Electrical Characteristics

T

A

= 0

°

C to +70

°

C, V

DDQ3

= 3.3V±5%,V

DDQ2

= 2.5V

±

5%, f

XTL

= 14.31818 MHz

AC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the

clock output.

CPU Clock Outputs, CPU0:1 (Lump Capacitance Test Load = 20 pF)

Parameter

t

P

t

H

t

L

t

R

t

F

t

D

Description

Period

Test Condition/Comments

Measured on rising edge at 1.25V

CPU = 66.6 MHz

CPU = 100 MHz

Unit

ns

Min.

15

Typ.

Max.

15.5

Min.

10

Typ.

Max.

10.5

High Time

Duration of clock cycle above 2.0V

5.2

3.0

ns

Low Time

Duration of clock cycle below 0.4V

5.0

2.8

ns

Output Rise Time

Measured from 0.4V to 2.0V

0.4

1.6

0.4

1.6

V/ns

Output Fall Time

Measured from 2.0V to 0.4V

0.4

1.6

0.4

1.6

V/ns

Duty Cycle

Measured on rising and falling edge at

1.25V

45

55

45

55

%

t

JC

Jitter, Cycle-to-Cycle

Measured on rising edge at 1.25V. Max-

imum difference of cycle time between

two adjacent cycles.

200

250

ps

t

SK

f

ST

Output Skew

Measured on rising edge at 1.25V

175

175

ps

Frequency Stabiliza-

tion from Power-up

(cold start)

Assumes full supply voltage reached

within 1 ms from power-up. Short cycles

exist prior to frequency stabilization.

3

3

ms

Z

o

AC Output Impedance

Average value during switching transi-

tion. Used for determining series termi-

nation value.

13.5

13.5

PCI Clock Outputs, PCI1:5 and PCI_F (Lump Capacitance Test Load = 30 pF

Parameter

t

P

t

H

t

L

t

R

t

F

t

D

t

JC

Description

Test Condition/Comments

Measured on rising edge at 1.5V

CPU = 66.6/100 MHz

Unit

ns

Min.

30

Typ.

Max.

Period

High Time

Duration of clock cycle above 2.4V

12

ns

Low Time

Duration of clock cycle below 0.4V

12

ns

Output Rise Edge Rate

Measured from 0.4V to 2.4V

1

4

V/ns

Output Fall Edge Rate

Measured from 2.4V to 0.4V

1

4

V/ns

Duty Cycle

Measured on rising and falling edge at 1.5V

45

55

%

Jitter, Cycle-to-Cycle

Measured on rising edge at 1.5V. Maximum

difference of cycle time between two adjacent cycles.

250

ps

t

SK

t

O

Output Skew

Measured on rising edge at 1.5V

500

ps

CPU to PCI Clock Skew

Covers all CPU/PCI outputs. Measured on rising

edge at 1.5V. CPU leads PCI output.

1.5

4

ns

f

ST

Frequency Stabilization

from Power-up (cold

start)

Assumes full supply voltage reached within 1 ms

from power-up. Short cycles exist prior to frequency

stabilization.

3

ms

Z

o

AC Output Impedance

Average value during switching transition. Used for

determining series termination value.

30

相关PDF资料 |

PDF描述 |

|---|---|

| W48C111-17 | 100-MHz Mobile Motherboard System Clock(100-MHz 移动主板系统时钟) |

| W48C111 | Frequency Generator for Integrated Core Logic |

| W48C20 | Audio Subsystem Clock Generator(音频子系统时钟发生器) |

| W48C55A | Frequency Synthesizers(频率合成器) |

| W48C54A | Frequency Synthesizers(频率合成器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W48C111-16H | 功能描述:IC CLOCK GEN FREQ MOD 28-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| W48C111-16HT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| W48C111-17 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:100-MHz Mobile Motherboard System Clock |

| W48C20 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Audio Subsystem Clock Generator |

| W48C20-08G | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Miscellaneous Clock Generator |

发布紧急采购,3分钟左右您将得到回复。