- 您现在的位置:买卖IC网 > PDF目录68559 > W972GG8JB-18 (WINBOND ELECTRONICS CORP) 256M X 8 DDR DRAM, 0.35 ns, PBGA60 PDF资料下载

参数资料

| 型号: | W972GG8JB-18 |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | 256M X 8 DDR DRAM, 0.35 ns, PBGA60 |

| 封装: | 11 X 11.50 MM, ROHS COMPLIANT, WBGA-60 |

| 文件页数: | 57/86页 |

| 文件大小: | 1466K |

| 代理商: | W972GG8JB-18 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页当前第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

W972GG8JB

Publication Release Date: Feb. 18, 2011

- 60 -

Revision A02

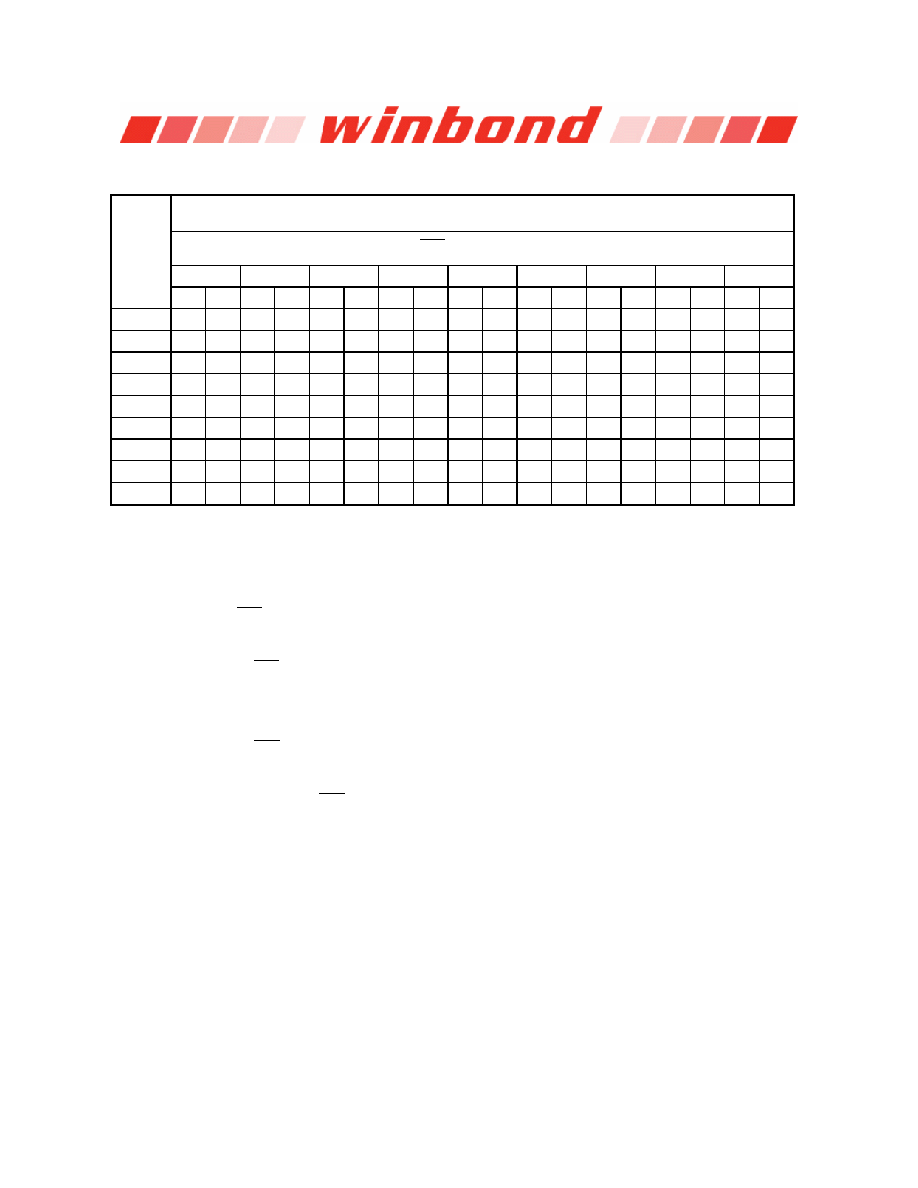

44. Data setup and hold time derating.

DDR2-667, DDR2-800 and DDR2-1066 tDS/tDH derating with differential data strobe

DQ

Slew

Rate

(V/nS)

ΔtDS, ΔtDH derating values for DDR2-667, DDR2-800 and DDR2-1066 (All units in pS; the note applies to

the entire table)

DQS/ DQS Differential Slew Rate

4.0 V/nS

3.0 V/nS

2.0 V/nS

1.8 V/nS

1.6 V/nS

1.4 V/nS

1.2 V/nS

1.0 V/nS

0.8 V/nS

ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH ΔtDS ΔtDH

2.0

100

45

100

45

100

45

-

1.5

67

21

67

21

67

21

79

33

-

1.0

0

12

24

-

0.9

-

-5

-14

-5

-14

7

-2

19

10

31

22

-

0.8

-

-13

-31

-1

-19

11

-7

23

5

35

17

-

0.7

-

-10

-42

2

-30

14

-18

26

-6

38

6

-

0.6

-

-10

-59

2

-47

14

-35

26

-23

38

-11

0.5

-

-24

-89

-12

-77

0

-65

12

-53

0.4

-

-52

-140

-40

-128

-28

-116

For all input signals the total tDS (setup time) and tDH (hold time) required is calculated by adding the data sheet tDS(base) and

tDH(base) value to the ΔtDS and ΔtDH derating value respectively. Example: tDS (total setup time) = tDS(base) + ΔtDS.

Setup (tDS) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VREF(dc) and the first

crossing of VIH(ac)min. Setup (tDS) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of

VREF(dc) and the first crossing of VIL(ac)max. If the actual signal is always earlier than the nominal slew rate line between

shaded VREF(dc) to AC region, use nominal slew rate for derating value. See Figure 24 Illustration of nominal slew rate for

tDS (differential DQS, DQS ).

If the actual signal is later than the

nominal slew rate line anywhere between shaded VREF(dc) to AC region, the slew rate of a

tangent line to the actual signal from the AC level to DC level is used for derating value. See Figure 25 Illustration of tangent line

for tDS (differential DQS, DQS ).

Hold (tDH) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VIL(dc)max and the first

crossing of VREF(dc). Hold (tDH) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of

VIH(dc)min and the first crossing of VREF(dc). If the actual signal is always later than the nominal slew rate line between

shaded

DC level to VREF(dc) region, use nominal slew rate for derating value. See Figure 26 Illustration of nominal slew rate

for tDH (differential DQS, DQS ).

If the actual signal is earlier than the nominal slew rate line anyw

here between shaded DC to VREF(dc) region, the slew rate of

a tangent line to the actual signal from the DC level to VREF(dc) level is used for derating value. See Figure 27 Illustration of

tangent line for tDH (differential DQS, DQS ).

Although for slow slew rates the total setup time might be negative (i.e. a valid input signal will not have reached VIH/IL(ac) at

the time of the rising clock transition) a valid input signal is still required to complete the transition and reach VIH/IL(ac).

For slew rates in between the values listed in above DDR2-667, DDR2-800 and DDR2-1066 tDS/tDH derating with differential

data strobe table, the derating values may be obtained by linear interpolation.

These values are typically not subject to production test. They are verified by design and characterization.

相关PDF资料 |

PDF描述 |

|---|---|

| W9751G6JB-18 | 32M X 16 DDR DRAM, 0.35 ns, PBGA84 |

| W981204AH-8H | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| W981216BH75L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| W981216BH-75 | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| W9812G2IH-6 | 4M X 32 SYNCHRONOUS DRAM, 5 ns, PDSO86 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W972GG8JB-25 | 制造商:Winbond Electronics Corp 功能描述:2GMB DDRII 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 60WBGA |

| W972GG8JB-25I | 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 2.5NS 80WBGA |

| W972GG8JB-3 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 2G-Bit 256Mx8 1.8V 60-Pin WBGA 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 2GBIT 3NS |

| W9751G6IB-25 | 功能描述:IC DDR2-800 SDRAM 512MB 84-WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.173",4.40mm 宽) 供应商设备封装:8-MFP 包装:带卷 (TR) |

| W9751G6JB | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM |

发布紧急采购,3分钟左右您将得到回复。