参数资料

| 型号: | X1205V8IZT1 |

| 厂商: | Intersil |

| 文件页数: | 22/22页 |

| 文件大小: | 0K |

| 描述: | IC RTC/CALENDAR 2-WIRE 8-TSSOP |

| 标准包装: | 2,500 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年 |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | I²C,2 线串口 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电压 - 电源,电池: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 带卷 (TR) |

9

FN8097.3

May 2, 2006

When there is a match, an alarm flag is set. The occur-

rence of an alarm can be determined by polling the

AL0 and AL1 bits or by enabling the IRQ output, using

it as hardware flag.

The alarm enable bits are located in the MSB of the

particular register. When all enable bits are set to ‘0’,

there are no alarms.

– The user can set the X1205 to alarm every Wednes-

day at 8:00 AM by setting the EDWn*, the EHRn*

and EMNn* enable bits to ‘1’ and setting the DWAn*,

HRAn* and MNAn* Alarm registers to 8:00AM

Wednesday.

– A daily alarm for 9:30PM results when the EHRn*

and EMNn* enable bits are set to ‘1’ and the HRAn*

and MNAn* registers are set to 9:30PM.

*n = 0 for Alarm 0: N = 1 for Alarm 1

REAL TIME CLOCK REGISTERS

Clock/Calendar Registers (SC, MN, HR, DT, MO, YR)

These registers depict BCD representations of the

time. As such, SC (Seconds) and MN (Minutes) range

from 00 to 59, HR (Hour) is 1 to 12 with an AM or PM

indicator (H21 bit) or 0 to 23 (with MIL = 1), DT (Date)

is 1 to 31, MO (Month) is 1 to 12, YR (Year) is 0 to 99.

Date of the Week Register (DW)

This register provides a Day of the Week status and

uses three bits DY2 to DY0 to represent the seven

days of the week. The counter advances in the cycle

0-1-2-3-4-5-6-0-1-2-… The assignment of a numerical

value to a specific day of the week is arbitrary and may

be decided by the system software designer. The

default value is defined as ‘0’.

24 Hour Time

If the MIL bit of the HR register is 1, the RTC uses a

24-hour format. If the MIL bit is 0, the RTC uses a 12-

hour format and H21 bit functions as an AM/PM indi-

cator with a ‘1’ representing PM. The clock defaults to

standard time with H21 = 0.

Leap Years

Leap years add the day February 29 and are defined

as those years that are divisible by 4. Years divisible

by 100 are not leap years, unless they are also divisi-

ble by 400. This means that the year 2000 is a leap

year, the year 2100 is not. The X1205 does not correct

for the leap year in the year 2100.

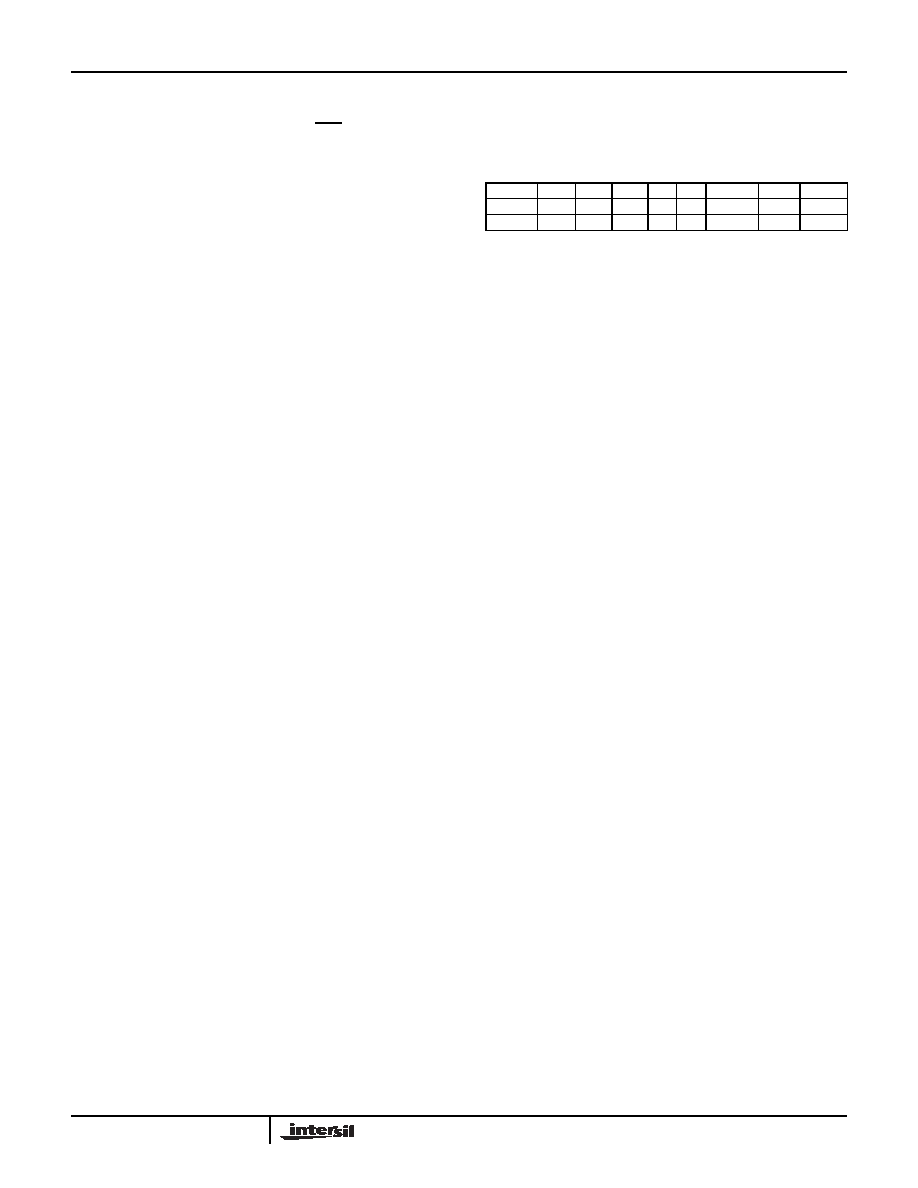

STATUS REGISTER (SR)

The Status Register is located in the CCR memory

map at address 003Fh. This is a volatile register only

and is used to control the WEL and RWEL write

enable latches, read two power status and two alarm

bits. This register is separate from both the array and

the Clock/Control Registers (CCR).

Table 1. Status Register (SR)

BAT: Battery Supply-Volatile

This bit set to “1” indicates that the device is operating

from VBACK, not VCC. It is a read-only bit and is

set/reset by hardware (X1205 internally). Once the

device begins operating from VCC, the device sets this

bit to “0”.

AL1, AL0: Alarm bits-Volatile

These bits announce if either alarm 0 or alarm 1 match

the real time clock. If there is a match, the respective

bit is set to ‘1’. The falling edge of the last data bit in a

SR Read operation resets the flags. Note: Only the AL

bits that are set when an SR read starts will be reset.

An alarm bit that is set by an alarm occurring during an

SR read operation will remain set after the read opera-

tion is complete.

RWEL: Register Write Enable Latch-Volatile

This bit is a volatile latch that powers up in the LOW

(disabled) state. The RWEL bit must be set to “1” prior

to any writes to the Clock/Control Registers. Writes to

RWEL bit do not cause a nonvolatile write cycle, so

the device is ready for the next operation immediately

after the stop condition. A write to the CCR requires

both the RWEL and WEL bits to be set in a specific

sequence. The RWEL bit is reset by the completion of

a nonvolatile write cycle.

WEL: Write Enable Latch-Volatile

The WEL bit controls the access to the CCR and

memory array during a write operation. This bit is a

volatile latch that powers up in the LOW (disabled)

state. While the WEL bit is LOW, writes to the CCR or

any array address will be ignored (no acknowledge will

be issued after the Data Byte). The WEL bit is set by

writing a “1” to the WEL bit and zeroes to the other bits

of the Status Register. Once set, WEL remains set

until either reset to 0 (by writing a “0” to the WEL bit

and zeroes to the other bits of the Status Register) or

until the part powers up again. Writes to WEL bit do

not cause a nonvolatile write cycle, so the device is

ready for the next operation immediately after the stop

condition.

Addr

7

6

5

4

3

2

1

0

003Fh

BAT

AL1

AL0

0

RWEL

WEL

RTCF

Default

0

1

X1205

相关PDF资料 |

PDF描述 |

|---|---|

| MCP4151T-503E/SN | IC POT DGTL SNGL 50K SPI 8SOIC |

| M83723/71W2232N | CONN RCPT 32POS WALL MT W/SCKT |

| MCP4151T-502E/MF | IC POT DGTL SNGL 5K SPI 8DFN |

| X1205V8IZ | IC RTC/CALENDAR 2-WIRE 8-TSSOP |

| MCP4151T-502E/SN | IC POT DGTL SNGL 5K SPI 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X1205V8T1 | 功能描述:IC RTC/CALENDAR 2-WIRE 8-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 实时时钟 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 类型:时钟/日历 特点:警报器,闰年,SRAM 存储容量:- 时间格式:HH:MM:SS(12/24 小时) 数据格式:YY-MM-DD-dd 接口:SPI 电源电压:2 V ~ 5.5 V 电压 - 电源,电池:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WDFN 裸露焊盘 供应商设备封装:8-TDFN EP 包装:管件 |

| X1205V8Z | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:2-Wire RTC Real Time Clock/Calendar |

| X1205V8ZT1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:2-Wire RTC Real Time Clock/Calendar |

| X1210MKX7R8BB564 | 制造商:Yageo / Phycomp 功能描述:0.56uF 25V SM CAP-X2Y FILTER 1210 X7R 20% Ni Barr w/100% Tin - free partial T/R at 500. |

| X121198-ISD | 制造商:Honeywell Sensing and Control 功能描述:RESISTIVE & OPTICAL |

发布紧急采购,3分钟左右您将得到回复。