- 您现在的位置:买卖IC网 > PDF目录371213 > X25128SI SPI Serial E 2 PROM with Block Lock TM Protection PDF资料下载

参数资料

| 型号: | X25128SI |

| 英文描述: | SPI Serial E 2 PROM with Block Lock TM Protection |

| 中文描述: | SPI串行e的2座门锁TM保护胎膜早破 |

| 文件页数: | 1/15页 |

| 文件大小: | 77K |

| 代理商: | X25128SI |

SPI Serial E

2

PROM with Block Lock

TM

Protection

128K

16K x 8 Bit

3091-2.9 5/14/97 T2/C0/D2 SH

Xicor Inc. 1994, 1995, 1996 Patents Pending

Characteristics subject to change without notice

1

X25128

A

PPLICATION

A V A I L A B L E

AN61

N

OTE

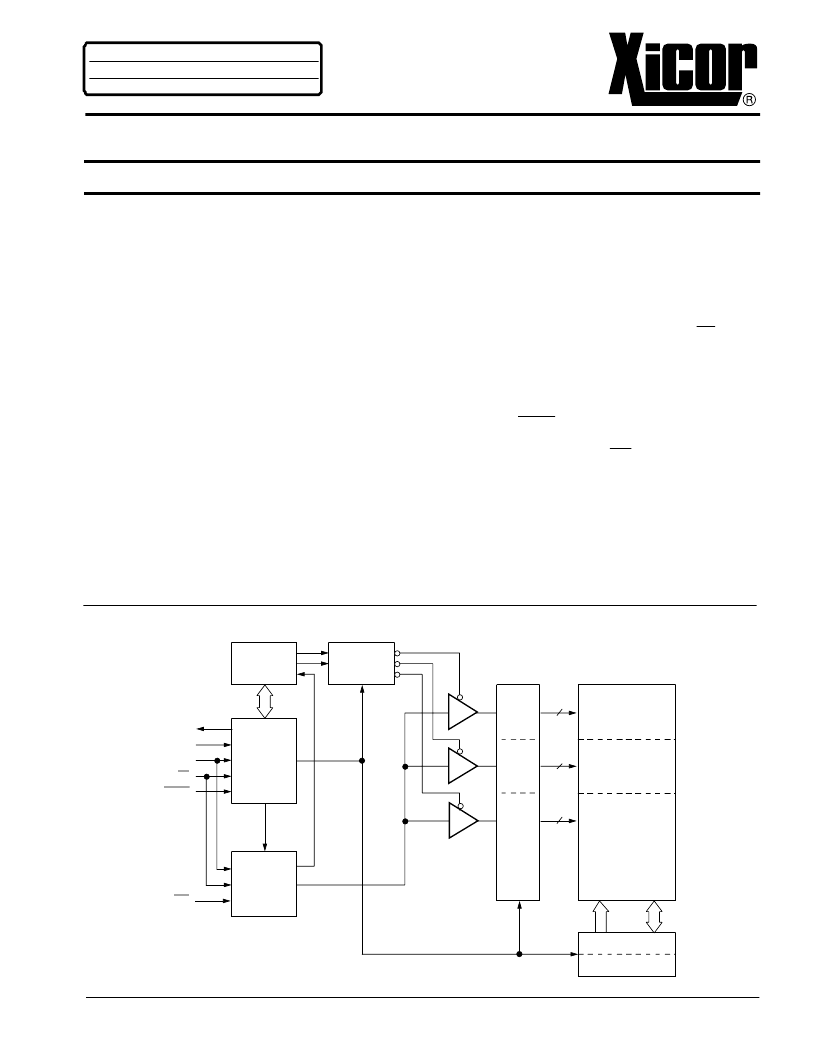

FUNCTIONAL DIAGRAM

COMMAND

DECODE

AND

CONTROL

LOGIC

WRITE

CONTROL

AND

TIMING

LOGIC

WRITE

PROTECT

LOGIC

X DECODE

LOGIC

16K BYTE

ARRAY

16 X 256

Y DECODE

DATA REGISTER

SO

SI

SCK

CS

HOLD

WP

8

32

32 X 256

16 X 256

3091 FM F01

128

128

256

STATUS

REGISTER

FEATURES

2MHz Clock Rate

SPI Modes (0,0 & 1,1)

16K X 8 Bits

—32 Byte Page Mode

Low Power CMOS

—<1

μ

A Standby Current

—<5mA Active Current

2.7V To 5.5V Power Supply

Block Lock Protection

—Protect 1/4, 1/2 or all of E

Built-in Inadvertent Write Protection

—Power-Up/Power-Down protection circuitry

—Write Enable Latch

—Write Protect Pin

Self-Timed Write Cycle

—5ms Write Cycle Time (Typical)

High Reliability

—Endurance: 100,000 cycles

—Data Retention: 100 Years

—ESD protection: 2000V on all pins

14-Lead SOIC Package

16-Lead SOIC Package

8-Lead PDIP Package

2

PROM Array

DESCRIPTION

The X25128 is a CMOS 131,072-bit serial E

internally organized as 16K x 8. The X25128 features

a Serial Peripheral Interface (SPI) and software

protocol allowing operation on a simple three-wire bus.

The bus signals are a clock input (SCK) plus separate

data in (SI) and data out (SO) lines. Access to the

device is controlled through a chip select (CS) input,

allowing any number of devices to share the same

bus.

2

PROM,

The X25128 also features two additional inputs that

provide the end user with added flexibility. By

asserting the HOLD input, the X25128 will ignore tran-

sitions on its inputs, thus allowing the host to service

higher priority interrupts. The WP input can be used as

a hardwire input to the X25128 disabling all write

attempts to the status register, thus providing a mech-

anism for limiting end user capability of altering 0, 1/4,

1/2 or all of the memory.

The X25128 utilizes Xicor’s proprietary Direct Write

cell, providing a minimum endurance of 100,000

cycles and a minimum data retention of 100 years.

相关PDF资料 |

PDF描述 |

|---|---|

| X25128SM | SPI Serial E 2 PROM with Block Lock TM Protection |

| X25128S-2.7 | SPI Serial E 2 PROM with Block Lock TM Protection |

| X25128PI-2.7 | SPI Serial E 2 PROM with Block Lock TM Protection |

| X25128SM-2.7 | CA3106ER24-11P |

| X25128Z | Ballast Control, Below Resonance Protection, Thermal Overload Protection, Protection from Failure to Strike, Programmable Preheat Time and Run Frequency, Programmable Deadtime, Automatic Restart for Lamp Exchange in a 16-pin DIP package; Similar to IR21571 with Lead Free Packaging |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X25128SI-2.7 | 制造商:ICMIC 制造商全称:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block Lock Protection |

| X25128SIG | 制造商:ICMIC 制造商全称:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block Lock Protection |

| X25128SIG-2.7 | 制造商:ICMIC 制造商全称:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block Lock Protection |

| X25128SM | 制造商:XICOR 制造商全称:Xicor Inc. 功能描述:SPI Serial E 2 PROM with Block Lock TM Protection |

| X25128SM-2.7 | 制造商:ICMIC 制造商全称:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM with Block Lock Protection |

发布紧急采购,3分钟左右您将得到回复。