参数资料

| 型号: | X40034V14I-CT1 |

| 厂商: | Intersil |

| 文件页数: | 12/23页 |

| 文件大小: | 0K |

| 描述: | IC VOLTAGE MONITOR TRPL 14-TSSOP |

| 标准包装: | 2,500 |

| 类型: | 多压监控器 |

| 监视电压数目: | 3 |

| 输出: | 推挽式,图腾柱 |

| 复位: | 高有效 |

| 复位超时: | 可调节/可选择 |

| 电压 - 阀值: | 1V,2.9V,4.6V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 带卷 (TR) |

�� �

�

�

�X40030,� X40031,� X40034,� X40035�

�MRF:� Manual� Reset� Fail� Bit� (Volatile)�

�The� MRF� bit� will� be� set� to� “0”� when� Manual� Reset� input� goes�

�active.�

�WDF:� Watchdog� Timer� Fail� Bit� (Volatile)�

�The� WDF� bit� will� be� set� to� “0”� when� the� WDO� goes� active.�

�LV1F:� Low� V� CC� Reset� Fail� Bit� (Volatile)�

�The� LV1F� bit� will� be� set� to� “0”� when� V� CC� (V1MON)� falls�

�below� V� TRIP1� .�

�LV2F:� Low� V2MON� Reset� Fail� Bit� (Volatile)�

�The� LV2F� bit� will� be� set� to� “0”� when� V2MON� falls� below�

�V� TRIP2� .�

�LV3F:� Low� V3MON� Reset� Fail� Bit� (Volatile)�

�The� LV3F� bit� will� be� set� to� “0”� when� the� V3MON� falls� below�

�V� TRIP3� .�

�Serial� Interface�

�Interface� Conventions�

�The� device� supports� a� bidirectional� bus� oriented� protocol.� The�

�protocol� defines� any� device� that� sends� data� onto� the� bus� as� a�

�transmitter,� and� the� receiving� device� as� the� receiver.� The�

�device� controlling� the� transfer� is� called� the� master� and� the�

�device� being� controlled� is� called� the� slave.� The� master� always�

�initiates� data� transfers,� and� provides� the� clock� for� both�

�transmit� and� receive� operations.� Therefore,� the� devices� in� this�

�family� operate� as� slaves� in� all� applications.�

�Serial� Clock� and� Data�

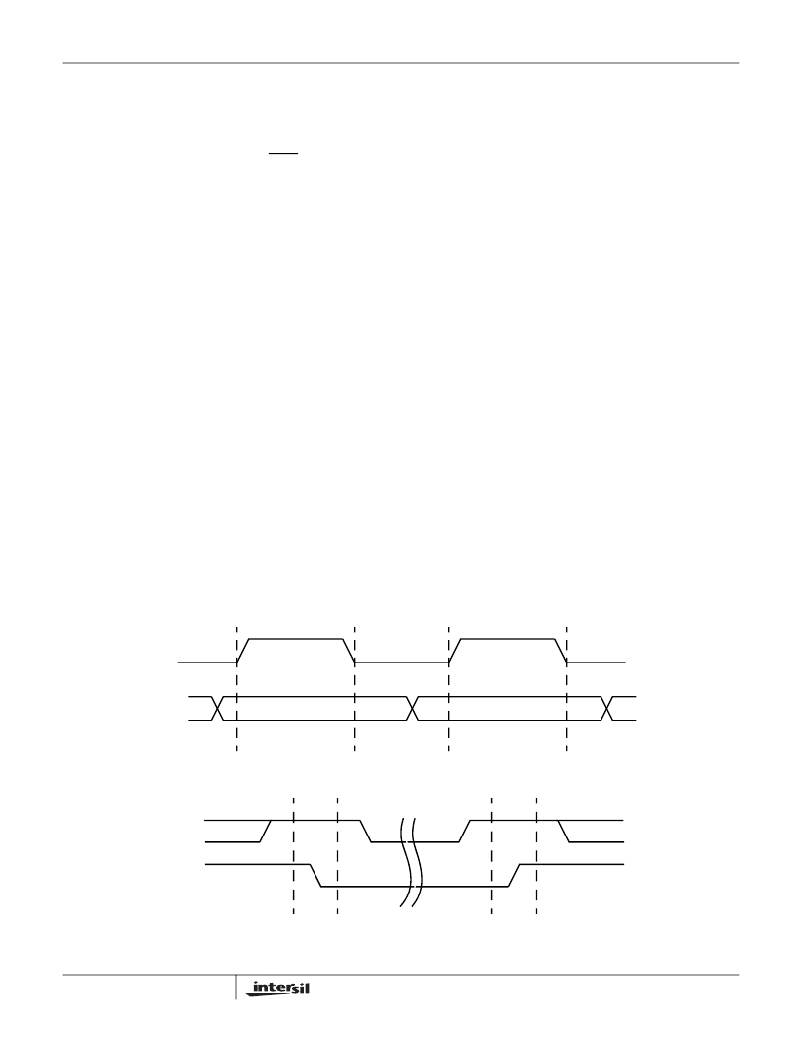

�Data� states� on� the� SDA� line� can� change� only� during� SCL�

�LOW.� SDA� state� changes� during� SCL� HIGH� are� reserved� for�

�indicating� start� and� stop� conditions.� See� Figure� 7.�

�SCL�

�SDA�

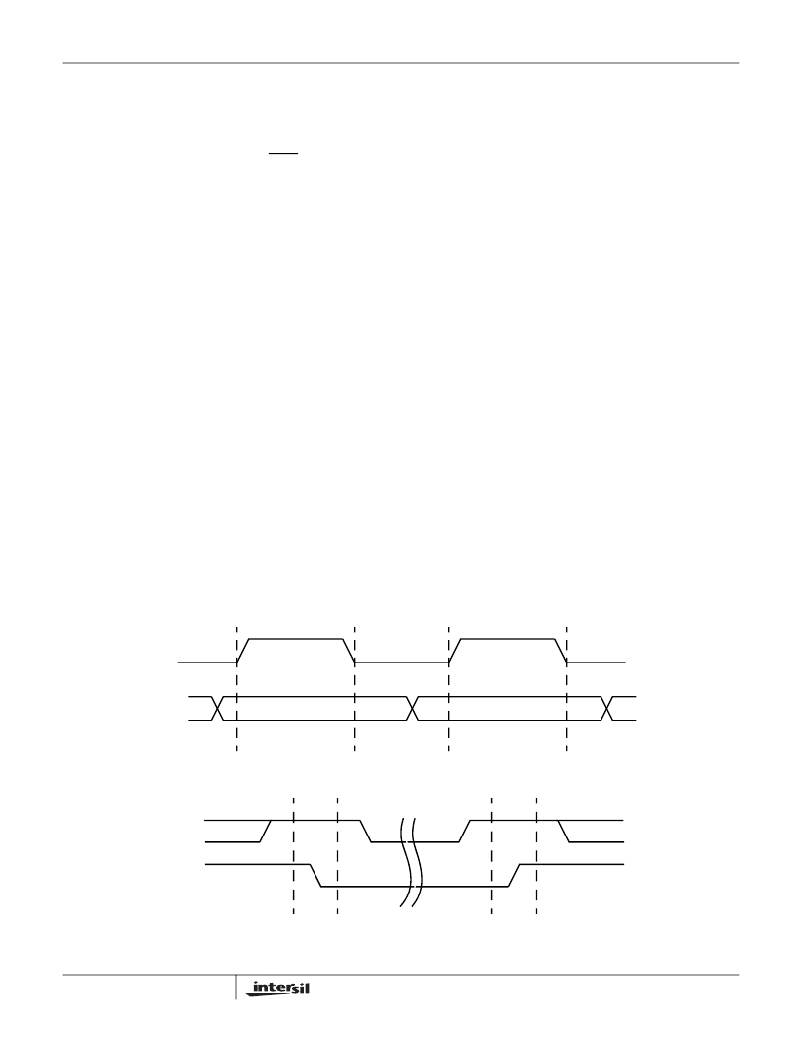

�Serial� Start� Condition�

�All� commands� are� preceded� by� the� start� condition,� which� is� a�

�HIGH� to� LOW� transition� of� SDA� when� SCL� is� HIGH.� The�

�device� continuously� monitors� the� SDA� and� SCL� lines� for� the�

�start� condition� and� will� not� respond� to� any� command� until�

�this� condition� has� been� met.� See� Figure� 8.�

�Serial� Stop� Condition�

�All� communications� must� be� terminated� by� a� stop� condition,�

�which� is� a� LOW� to� HIGH� transition� of� SDA� when� SCL� is�

�HIGH.� The� stop� condition� is� also� used� to� place� the� device�

�into� the� Standby� power� mode� after� a� read� sequence.� A� stop�

�condition� can� only� be� issued� after� the� transmitting� device�

�has� released� the� bus.� See� Figure� 8.�

�Serial� Acknowledge�

�Acknowledge� is� a� software� convention� used� to� indicate�

�successful� data� transfer.� The� transmitting� device,� either�

�master� or� slave,� will� release� the� bus� after� transmitting� 8-bits.�

�During� the� ninth� clock� cycle,� the� receiver� will� pull� the� SDA�

�line� LOW� to� acknowledge� that� it� received� the� 8-bits� of� data.�

�See� Figure� 9.�

�The� device� will� respond� with� an� acknowledge� after�

�recognition� of� a� start� condition� and� if� the� correct� Device�

�Identifier� and� Select� bits� are� contained� in� the� Slave� Address�

�Byte.� If� a� write� operation� is� selected,� the� device� will� respond�

�with� an� acknowledge� after� the� receipt� of� each� subsequent�

�8-bit� word.� The� device� will� acknowledge� all� incoming� data�

�and� address� bytes,� except� for� the� Slave� Address� Byte� when�

�the� Device� Identifier� and/or� Select� bits� are� incorrect.�

�.�

�DATA� STABLE�

�DATA� CHANGE�

�DATA� STABLE�

�FIGURE� 7.� VALID� DATA� CHANGES� ON� THE� SDA� BUS�

�SCL�

�SDA�

�START�

�STOP�

�FIGURE� 8.� VALID� START� AND� STOP� CONDITIONS�

�12�

�FN8114.2�

�August� 25,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6363IRTZ | IC CONTROLLER VR12 48TQFN |

| RBM44DSES-S243 | CONN EDGECARD 88POS .156 EYELET |

| X40035S14I-AT1 | IC VOLTAGE MONITOR TRPL 14-SOIC |

| RSM22DSEI-S243 | CONN EDGECARD 44POS .156 EYELET |

| X40035S14I-A | IC VOLTAGE MONITOR TRPL 14-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X40034V14IZ-A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

| X40034V14IZ-B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

| X40034V14Z-A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

| X40034V14Z-B | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

| X40034VA | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple Voltage Monitor with Integrated CPU Supervisor |

发布紧急采购,3分钟左右您将得到回复。