- 您现在的位置:买卖IC网 > PDF目录297797 > X5323V14 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO14 PDF资料下载

参数资料

| 型号: | X5323V14 |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO14 |

| 封装: | PLASTIC, TSSOP-14 |

| 文件页数: | 19/21页 |

| 文件大小: | 200K |

| 代理商: | X5323V14 |

X5323/X5325

Characteristics subject to change without notice.

7 of 21

REV 1.1.2 11/13/01

www.xicor.com

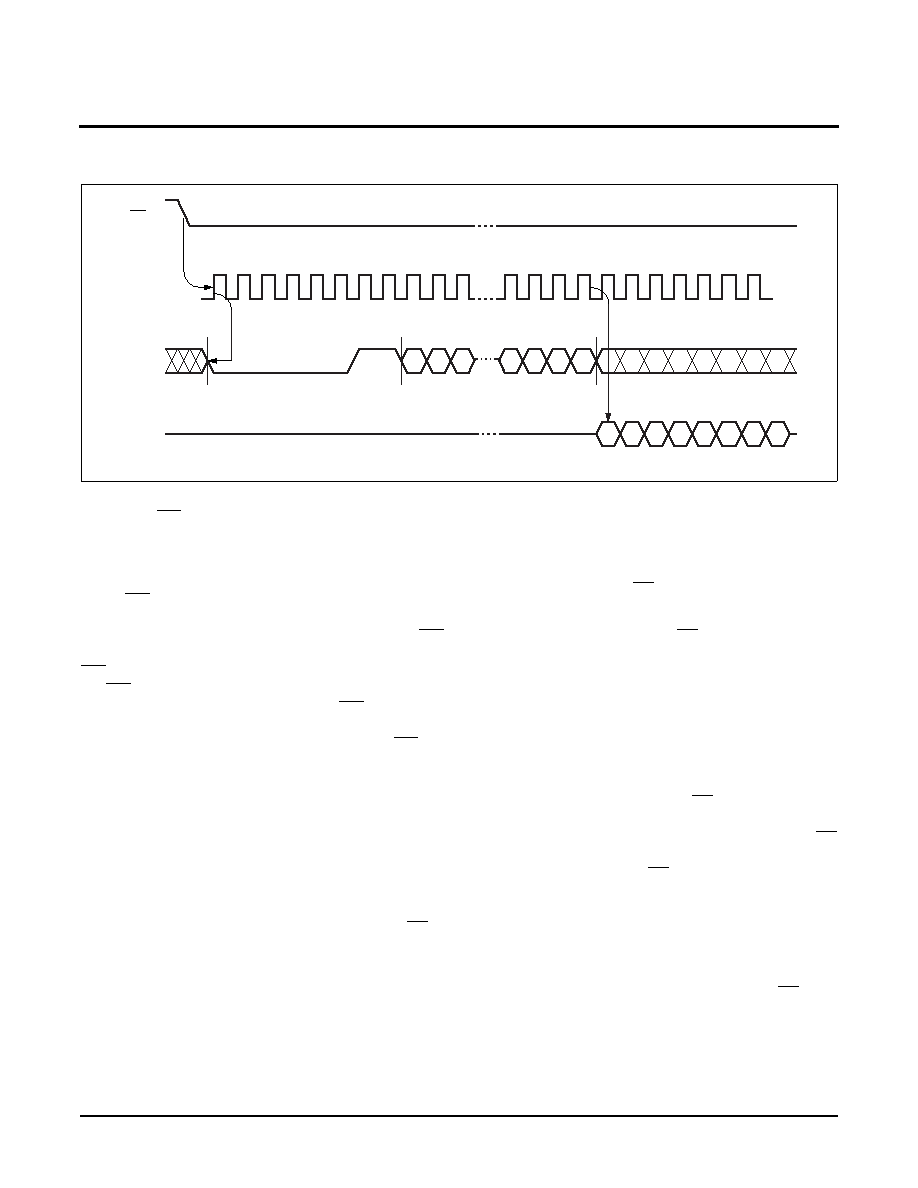

Figure 5. Read EEPROM Array Sequence

0123

456789

10

20 21 22 23 24 25

26 27 28 29 30

7

654321

0

Data Out

CS

SCK

SI

SO

MSB

High Impedance

Instruction

16 Bit Address

15 14 13

3

2

1

0

Setting the WP pin LOW while WPEN is a “1” while an

internal write cycle to the status register is in progress

will not stop this write operation, but the operation dis-

ables subsequent write attempts to the status register.

When WP is HIGH, all functions, including nonvolatile

writes to the status register operate normally. Setting

the WPEN bit in the status register to “0” blocks the WP

pin function, allowing writes to the status register when

WP is HIGH or LOW. Setting the WPEN bit to “1” while

the WP pin is LOW activates the programmable ROM

mode, thus requiring a change in the WP pin prior to

subsequent status register changes. This allows manu-

facturing to install the device in a system with WP pin

grounded and still be able to program the status regis-

ter. Manufacturing can then load conguration data,

manufacturing time and other parameters into the

EEPROM, then set the portion of memory to be pro-

tected by setting the block lock bits, and nally set the

“OTP mode” by setting the WPEN bit. Data changes

now require a hardware change.

Read Sequence

When reading from the EEPROM memory array, CS is

rst pulled low to select the device. The 8-bit READ

instruction is transmitted to the device, followed by the

16-bit address. After the READ opcode and address

are sent, the data stored in the memory at the selected

address is shifted out on the SO line. The data stored

in memory at the next address can be read sequen-

tially by continuing to provide clock pulses. The

address is automatically incremented to the next

higher address after each byte of data is shifted out.

When the highest address is reached, the address

counter rolls over to address $0000 allowing the read

cycle to be continued indenitely. The read operation is

terminated by taking CS high. Refer to the read

EEPROM Array Sequence (Figure 1).

To read the status register, the CS line is rst pulled low

to select the device followed by the 8-bit RDSR instruc-

tion. After the RDSR opcode is sent, the contents of the

status register are shifted out on the SO line. Refer to

the read status register sequence (Figure 2).

Write Sequence

Prior to any attempt to write data into the device, the

“Write Enable” Latch (WEL) must rst be set by issuing

the WREN instruction (Figure 3). CS is rst taken LOW,

then the WREN instruction is clocked into the device.

After all eight bits of the instruction are transmitted, CS

must then be taken HIGH. If the user continues the write

operation without taking CS HIGH after issuing the

WREN instruction, the write operation will be ignored.

To write data to the EEPROM memory array, the user

then issues the WRITE instruction followed by the 16

bit address and then the data to be written. Any

unused address bits are specied to be “0’s”. The

WRITE operation minimally takes 32 clocks. CS must

go low and remain low for the duration of the operation.

If the address counter reaches the end of a page and

the clock continues, the counter will roll back to the rst

address of the page and overwrite any data that may

have been previously written.

相关PDF资料 |

PDF描述 |

|---|---|

| X5323V14I-2.7T1 | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO14 |

| X5328V14I | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO14 |

| XAVAC25M/FS.0 | 25-25 CONTACT(S), PANEL MOUNT, MALE-FEMALE, RECTANGULAR ADAPTER |

| XAVAC25M/FS.5 | 25-25 CONTACT(S), PANEL MOUNT, MALE-FEMALE, RECTANGULAR ADAPTER |

| XAVAC25M/MD.0 | 25-25 CONTACT(S), PANEL MOUNT, MALE-MALE, RECTANGULAR ADAPTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X5323V14-1.8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X5323V14-2.7 | 功能描述:IC SUPERVISOR CPU 32K EE 14TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5323V14-2.7A | 功能描述:IC SUPERVISOR CPU 32K EE 14TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5323V14-2.7T1 | 功能描述:IC SUPERVISOR CPU 32K EE 14TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5323V14-4.5A | 功能描述:IC SUPERVISOR CPU 32K EE 14TSSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。