- 您现在的位置:买卖IC网 > PDF目录19483 > XA2C128-7CPG132I (Xilinx Inc)IC CPLD 128MC 100 I/O 132CSBGA PDF资料下载

参数资料

| 型号: | XA2C128-7CPG132I |

| 厂商: | Xilinx Inc |

| 文件页数: | 9/16页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 128MC 100 I/O 132CSBGA |

| 产品培训模块: | CoolRunner-II CPLD Starter Kit |

| 标准包装: | 360 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 7.0ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 8 |

| 宏单元数: | 128 |

| 门数: | 3000 |

| 输入/输出数: | 100 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 132-TFBGA,CSPBGA |

| 供应商设备封装: | 132-CSPBGA(8x8) |

| 包装: | 托盘 |

XA2C128 CoolRunner-II Automotive CPLD

DS554 (v1.2) June 9, 2009

Product Specification

2

R

The use of the clock divide (division by 2) and DualEDGE

flip-flop gives the resultant CoolCLOCK feature.

DataGATE is a method to selectively disable inputs of the

CPLD that are not of interest during certain points in time.

By mapping a signal to the DataGATE function, lower power

can be achieved due to reduction in signal switching.

Another feature that eases voltage translation is I/O bank-

ing. Two I/O banks are available on the CoolRunner-II Auto-

motive 128-macrocell device that permit easy interfacing to

3.3V, 2.5V, 1.8V, and 1.5V devices.

The CoolRunner-II Automotive 128-macrocell CPLD is I/O

compatible with various JEDEC I/O standards (see

Table 1). This device is also 1.5V I/O compatible with the

use of Schmitt-trigger inputs.

RealDigital Design Technology

Xilinx CoolRunner-II Automotive CPLDs are fabricated on a

0.18 micron process technology which is derived from lead-

ing edge FPGA product development. CoolRunner-II Auto-

motive CPLDs employ RealDigital technology, a design

technique that makes use of CMOS technology in both the

fabrication and design methodology. RealDigital technology

employs a cascade of CMOS gates to implement sum of

products instead of traditional sense amplifier methodology.

Due to this technology, Xilinx CoolRunner-II Automotive

CPLDs achieve both high-performance and low power oper-

ation.

Supported I/O Standards

The CoolRunner-II Automotive 128-macrocell device fea-

tures LVCMOS and LVTTL I/O implementations. See

Table 1 for I/O standard voltages. The LVTTL I/O standard is

a general purpose EIA/JEDEC standard for 3.3V applica-

tions that use an LVTTL input buffer and Push-Pull output

buffer. The LVCMOS standard is used in 3.3V, 2.5V, 1.8V

applications.

Table 1: I/O Standards for XA2C128

IOSTANDARD Attribute

Output VCCIO

Input VCCIO

LVTTL

3.3

LVCMOS33

3.3

LVCMOS25

2.5

LVCMOS18

1.8

LVCMOS15(1)

1.5

Notes:

1.

LVCMOS15 requires use of Schmitt-trigger inputs.

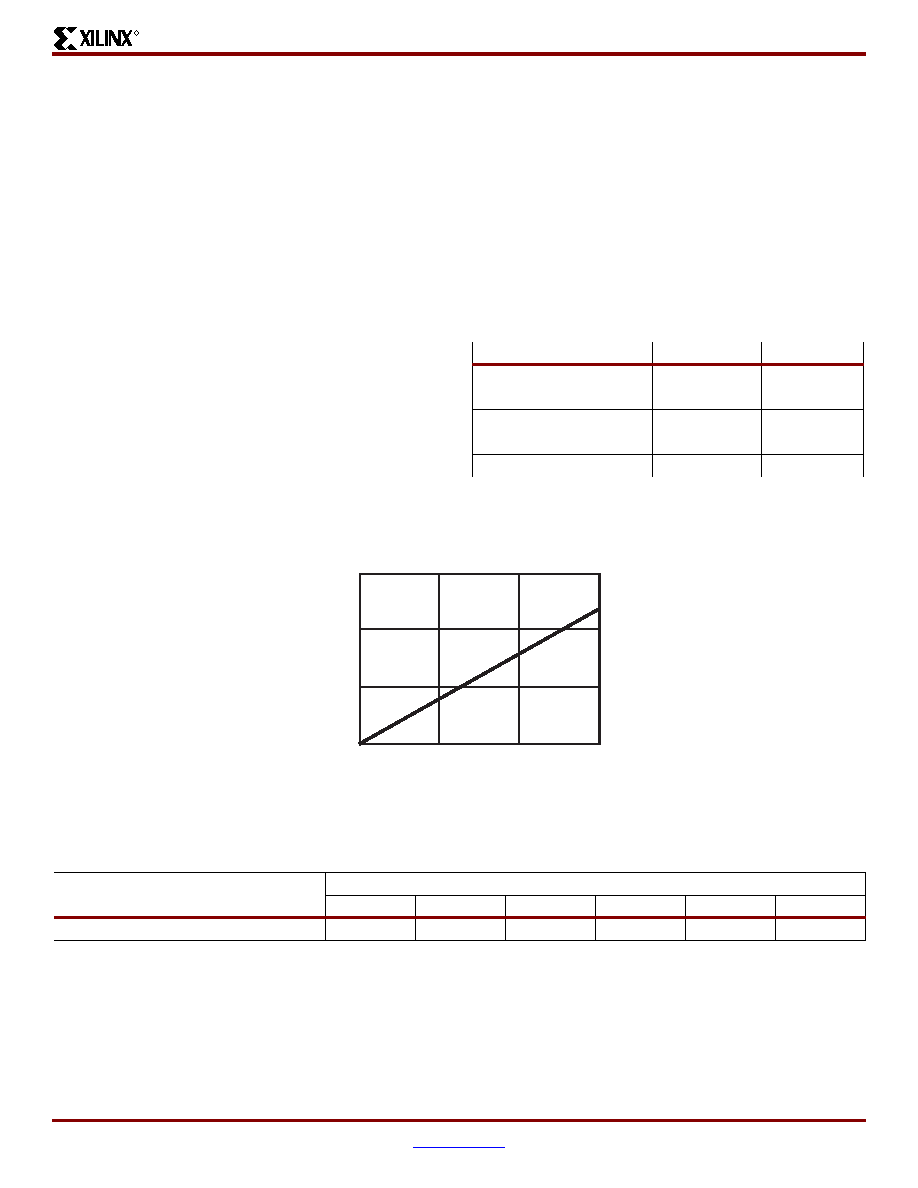

Figure 1: ICC vs Frequency

Table 2: ICC vs Frequency (LVCMOS 1.8V TA = 25°C)(1)

Frequency (MHz)

0

255075

100

150

Typical ICC (mA)

0.019

3.97

7.95

11.92

15.89

23.83

Notes:

1.

16-bit up/down, Resetable binary counter (one counter per function block).

Frequency (MHz)

DS554_01_052109

I CC

(mA)

0

150

100

50

20

0

10

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21375KSWZ-2B | IC DSP 32BIT 266MHZ 208-MQFP |

| EEM06DRKH | CONN EDGECARD 12POS DIP .156 SLD |

| SMK316B7682KF-T | CAP CER 6800PF 630V 10% X7R 1206 |

| ECC22DCAH | CONN EDGECARD 44POS R/A .100 SLD |

| XC95144XL-5TQ100C | IC CPLD 144 MCELL 3.3V 100-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA2C128-7VQG100I | 功能描述:IC CPLD 128MCELL 80 I/O 100VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XA2C128-8CPG132Q | 功能描述:IC CPLD 128MC 100 I/O 132CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XA2C128-8VQG100Q | 功能描述:IC CPLD 128MCELL 80 I/O 100VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:160 系列:ispMACH® 4000V 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:3 V ~ 3.6 V 逻辑元件/逻辑块数目:2 宏单元数:32 门数:- 输入/输出数:30 工作温度:-40°C ~ 130°C 安装类型:表面贴装 封装/外壳:44-TQFP 供应商设备封装:44-TQFP(10x10) 包装:托盘 |

| XA2C256 | 制造商:XILINX 制造商全称:XILINX 功能描述:CoolRunner-II Automotive CPLD |

| XA2C256-7TQG10I | 制造商:XILINX 制造商全称:XILINX 功能描述:CoolRunner-II Automotive CPLD |

发布紧急采购,3分钟左右您将得到回复。