- 您现在的位置:买卖IC网 > PDF目录19875 > XC17256EPCG20C (Xilinx Inc)IC PROM SERIAL 256K 20-PLCC PDF资料下载

参数资料

| 型号: | XC17256EPCG20C |

| 厂商: | Xilinx Inc |

| 文件页数: | 9/13页 |

| 文件大小: | 0K |

| 描述: | IC PROM SERIAL 256K 20-PLCC |

| 产品变化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 Product Discontinuation 28/Jul/2010 |

| 标准包装: | 46 |

| 可编程类型: | OTP |

| 存储容量: | 256Kb |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 20-LCC(J 形引线) |

| 供应商设备封装: | 20-PLCC |

| 包装: | 管件 |

XC1700E, XC1700EL, and XC1700L Series Configuration PROMs

DS027 (v3.5) June 25, 2008

Product Specification

5

R

FPGA Master Serial Mode Summary

The I/O and logic functions of the Configurable Logic Block

(CLB) and their associated interconnections are established

by a configuration program. The program is loaded either

automatically upon power up, or on command, depending on

the state of the three FPGA mode pins. In Master Serial

mode, the FPGA automatically loads the configuration

program from an external memory. The Xilinx PROMs have

been designed for compatibility with the Master Serial mode.

Upon power-up or reconfiguration, an FPGA enters the

Master Serial mode whenever all three of the FPGA mode-

select pins are Low (M0=0, M1=0, M2=0). Data is read from

the PROM sequentially on a single data line. Synchronization

is provided by the rising edge of the temporary signal CCLK,

which is generated during configuration.

Master Serial Mode provides a simple configuration interface.

Only a serial data line and two control lines are required to

configure an FPGA. Data from the PROM is read sequentially,

accessed via the internal address and bit counters which are

incremented on every valid rising edge of CCLK.

If the user-programmable, dual-function DIN pin on the

FPGA is used only for configuration, it must still be held at a

defined level during normal operation. The Xilinx FPGA

families take care of this automatically with an on-chip

default pull-up resistor.

Programming the FPGA With Counters

Unchanged upon Completion

When multiple FPGA-configurations for a single FPGA are

stored in a PROM, the OE pin should be tied Low. Upon

power-up, the internal address counters are reset and

configuration begins with the first program stored in

memory. Since the OE pin is held Low, the address

counters are left unchanged after configuration is complete.

Therefore, to reprogram the FPGA with another program,

the DONE line is pulled Low and configuration begins at the

last value of the address counters.

This method fails if a user applies RESET during the FPGA

configuration process. The FPGA aborts the configuration

and then restarts a new configuration, as intended, but the

PROM does not reset its address counter, since it never

saw a High level on its OE input. The new configuration,

therefore, reads the remaining data in the PROM and

interprets it as preamble, length count etc. Since the FPGA

is the master, it issues the necessary number of CCLK

pulses, up to 16 million (224) and DONE goes High.

However, the FPGA configuration is then completely wrong,

with potential contentions inside the FPGA and on its output

pins. This method must, therefore, never be used when

there is any chance of external reset during configuration.

Cascading Configuration PROMs

For multiple FPGAs configured as a daisy-chain, or for

future FPGAs requiring larger configuration memories,

cascaded PROMs provide additional memory. After the last

bit from the first PROM is read, the next clock signal to the

PROM asserts its CEO output Low and disables its DATA

line. The second PROM recognizes the Low level on its CE

input and enables its DATA output. See Figure 2, page 6.

After configuration is complete, the address counters of

all cascaded PROMs are reset if the FPGA RESET pin

goes Low, assuming the PROM reset polarity option has

been inverted.

To reprogram the FPGA with another program, the DONE

line goes Low and configuration begins where the address

counters had stopped. In this case, avoid contention

between DATA and the configured I/O use of DIN.

Standby Mode

The PROM enters a low-power standby mode whenever CE

is asserted High. The output remains in a high-impedance

state regardless of the state of the OE input.

Programming

The devices can be programmed on programmers supplied

by Xilinx or qualified third-party vendors. The user must

ensure that the appropriate programming algorithm and the

latest version of the programmer software are used. The

wrong choice can permanently damage the device.

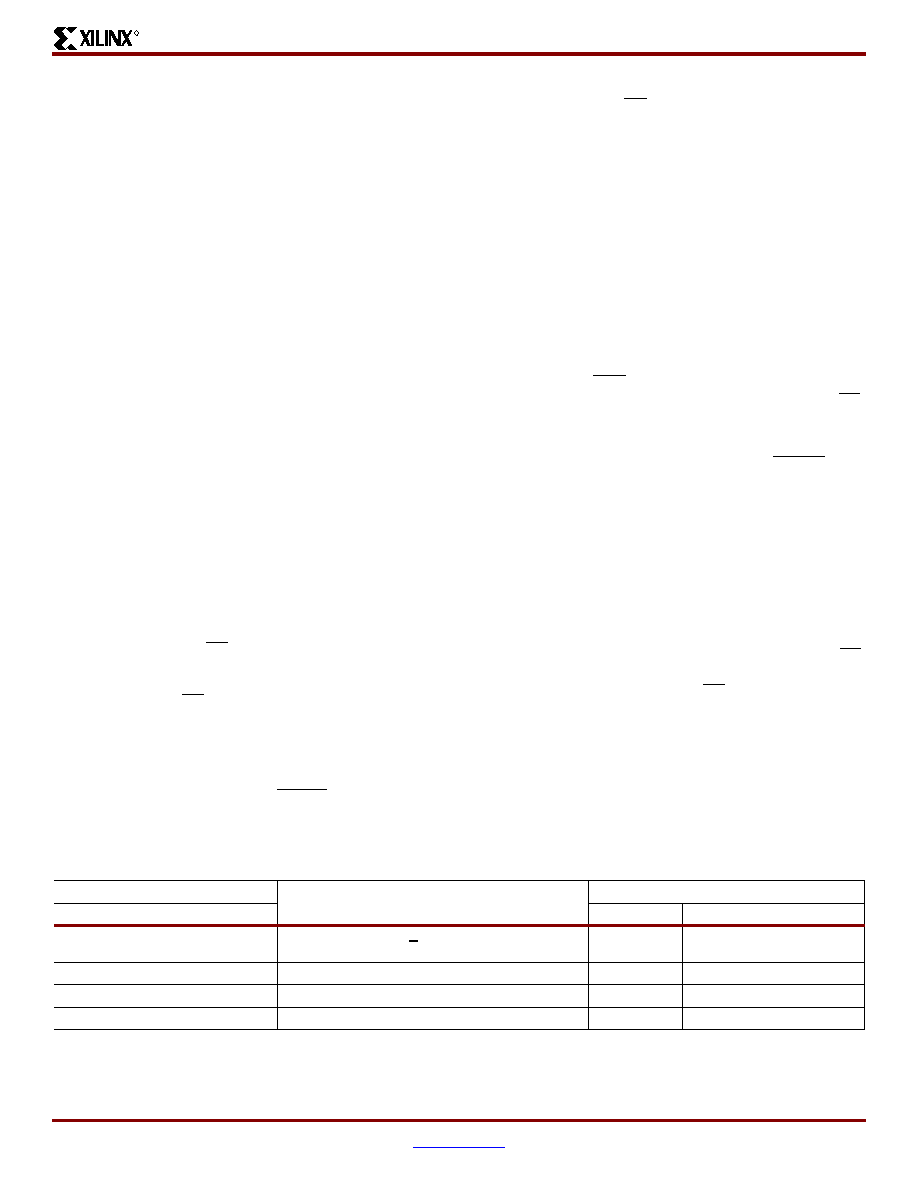

Table 1: Truth Table for XC1700 Control Inputs

Control Inputs

Internal Address

Outputs

RESET

CE

DATA

CEO

ICC

Inactive

Low

If address < TC(1): increment

If address > TC(2): don’t change

Active

High-Z

High

Low

Active

Reduced

Active

Low

Held reset

High-Z

High

Active

Inactive

High

Not changing

High-Z(3)

High

Standby

Active

High

Held reset

High-Z(3)

High

Standby

Notes:

1.

The XC1700 RESET input has programmable polarity.

2.

TC = Terminal Count = highest address value. TC + 1 = address 0.

3.

Pull DATA pin to GND or VCC to meet ICCS standby current.

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| XC17128EVOG8C | IC PROM SERIAL 128K 8-SOIC |

| VI-B12-CY-F3 | CONVERTER MOD DC/DC 15V 50W |

| XC17128EPCG20C | IC PROM SERIAL 128K 20-PLCC |

| MAX8840ELT30+T | IC REG LDO 3V .15A 6-UDFN |

| XC1701LPCG20I | IC PROM SERIAL 1K 20-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC17256EPD8C | 功能描述:IC SERIAL CFG PROM 256K 8-DIP RoHS:否 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

| XC17256EPD8I | 功能描述:IC PROM SER I-TEMP 256K 8-DIP RoHS:否 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

| XC17256EPDG8C | 功能描述:IC PROM SERIAL 256K 8-DIP RoHS:是 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

| XC17256EVO8C | 功能描述:IC SERIAL CFG PROM 256K 8-SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

| XC17256EVO8I | 功能描述:IC SERIAL CFG PROM 256K 8-SOIC RoHS:否 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。