- 您现在的位置:买卖IC网 > PDF目录19502 > XC2C32A-4VQG44C (Xilinx Inc)IC CPLD 32MCELL 21 I/O 44-VQFP PDF资料下载

参数资料

| 型号: | XC2C32A-4VQG44C |

| 厂商: | Xilinx Inc |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 32MCELL 21 I/O 44-VQFP |

| 标准包装: | 160 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 3.8ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 2 |

| 宏单元数: | 32 |

| 门数: | 750 |

| 输入/输出数: | 33 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-TQFP |

| 供应商设备封装: | 44-VQFP(10x10) |

| 包装: | 托盘 |

CoolRunner-II CPLD Family

6

DS090 (v3.1) September 11, 2008

Product Specification

R

software. The AIM minimizes both propagation delay and

power as it makes attachments to the various FBs.

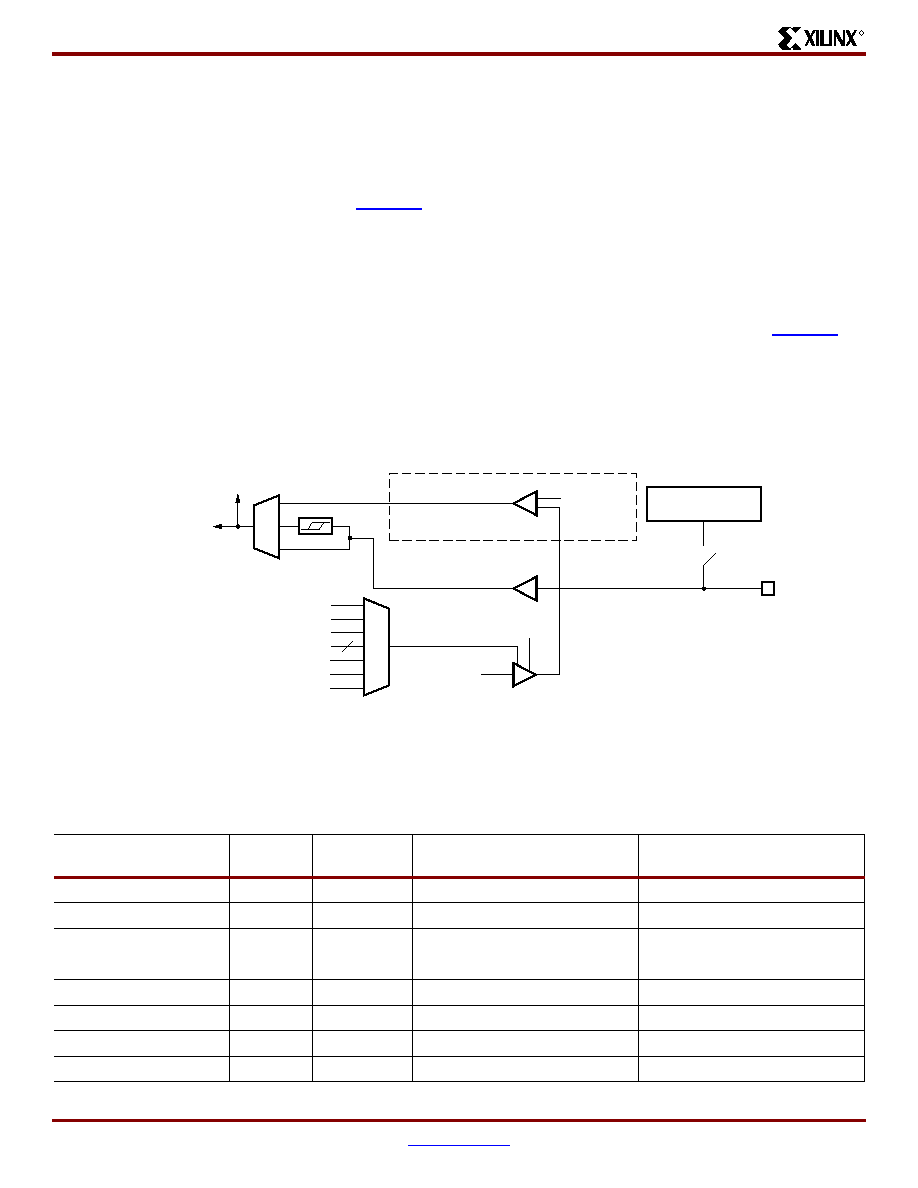

I/O Block

I/O blocks are primarily transceivers. However, each I/O is

either automatically compliant with standard voltage ranges

or can be programmed to become so. See XAPP382 for

detailed information on CoolRunner-II I/Os.

In addition to voltage levels, each input can selectively

arrive through Schmitt-trigger inputs. This adds a small time

delay, but substantially reduces noise on that input pin.

Approximately 500 mV of hysteresis is added when

Schmitt-trigger inputs are selected. All LVCMOS inputs can

have hysteresis input. Hysteresis also allows easy genera-

tion of external clock circuits. The Schmitt-trigger path is

patibility with I/O standards.

Outputs can be directly driven, 3-stated or open-drain con-

figured. A choice of slow or fast slew rate output signal is

also available. Table 5 summarizes various supported volt-

age standards associated with specific part capacities. All

inputs and disabled outputs are voltage tolerant up to 3.3V.

The CoolRunner-II family supports SSTL2-1, SSTL3-1 and

HSTL-1 high-speed I/O standards in the 128-macrocell and

larger devices. Figure 4 details the I/O pin, where it is noted

that the inputs requiring comparison to an external refer-

ence voltage are available. These I/O standards all require

VREF pins for proper operation. The CoolRunner-II CPLD

allows any I/O pin to act as a VREF pin, granting the board

layout engineer extra freedom when laying out the pins.

However, if VREF pin placement is not done properly, addi-

tional VREF pins might be required, resulting in a loss of

potential I/O pins or board re-work. See XAPP399 for

details regarding VREF pins and their placement.

VREF has pin-range requirements that must be observed.

The Xilinx software aids designers in remaining within the

proper pin range.

Table 5 summarizes the single ended I/O standard support

and shows which standards require VREF values and board

termination. VREF detail is given in specific data sheets.

Figure 4: CoolRunner-II CPLD I/O Block Diagram

Enabled

To Macrocell

Direct Input

To AIM

4

CTE

PTB

GTS[0:3]

CGND

Open Drain

From Macrocell

VCCIO

VREF

Disabled

Hysteresis

Available on 128 Macrocell Devices and Larger

Global termination

Pullup/Bus-Hold

DS090_04_121201

Table 5: CoolRunner-II CPLD I/O Standard Summary

IOSTANDARD

Attribute

VCCIO

Input VREF

Board Termination Voltage

(VTT)

Schmitt-trigger Support

LVTTL

3.3

N/A

Optional

LVCMOS33

3.3

N/A

Optional

LVCMOS25

2.5

N/A

Optional

LVCMOS18

1.8

N/A

Optional

LVCMOS15

1.5

N/A

Not optional

HSTL_1

1.5

0.75

Not optional

SSTL2_1

2.5

1.25

Not optional

SSTL3_1

3.3

1.5

Not optional

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B53-CY-F2 | CONVERTER MOD DC/DC 24V 50W |

| EBM18DRSI | CONN EDGECARD 36POS DIP .156 SLD |

| ACC35DRTN-S13 | CONN EDGECARD 70POS .100 EXTEND |

| XC9536XL-5VQG64C | IC CPLD 36MCELL 5NS 64-VQFP |

| ACC35DRTH-S13 | CONN EDGECARD 70POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2C32A-6CP56C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 750 GATES 32 MCRCLLS 300MHZ COMM 0.18UM 1 - Trays 制造商:Xilinx 功能描述:IC CPLD 32MC 5.5NS 56BGA 制造商:Xilinx 功能描述:IC CR-II CPLD 32MCELL 56-BGA |

| XC2C32A-6CP56I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 750 GATES 32 MCRCLLS 300MHZ IND 0.18UM 1. - Trays 制造商:Xilinx 功能描述:IC CPLD 32MC 5.5NS 56BGA 制造商:Xilinx 功能描述:IC CR-II CPLD 32MCELL 56-BGA |

| XC2C32A-6CPG56C | 功能描述:IC CR-II CPLD 32MCELL 56-CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XC2C32A-6CPG56I | 功能描述:IC CR-II CPLD 32MCELL 56-CSBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XC2C32A-6PC44C | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。