- 您现在的位置:买卖IC网 > PDF目录19834 > XC2C64A-7VQG100C (Xilinx Inc)IC CR-II CPLD 64MCELL 100-VQFP PDF资料下载

参数资料

| 型号: | XC2C64A-7VQG100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 12/16页 |

| 文件大小: | 0K |

| 描述: | IC CR-II CPLD 64MCELL 100-VQFP |

| 标准包装: | 90 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 6.7ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 4 |

| 宏单元数: | 64 |

| 门数: | 1500 |

| 输入/输出数: | 64 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-VQFP(14x14) |

| 包装: | 托盘 |

| 产品目录页面: | 600 (CN2011-ZH PDF) |

| 配用: | 122-1536-ND - KIT STARTER SPARTAN-3E 122-1532-ND - KIT DEVELOPMENT SPARTAN 3ADSP |

| 其它名称: | 122-1409 |

CoolRunner-II CPLD Family

DS090 (v3.1) September 11, 2008

Product Specification

R

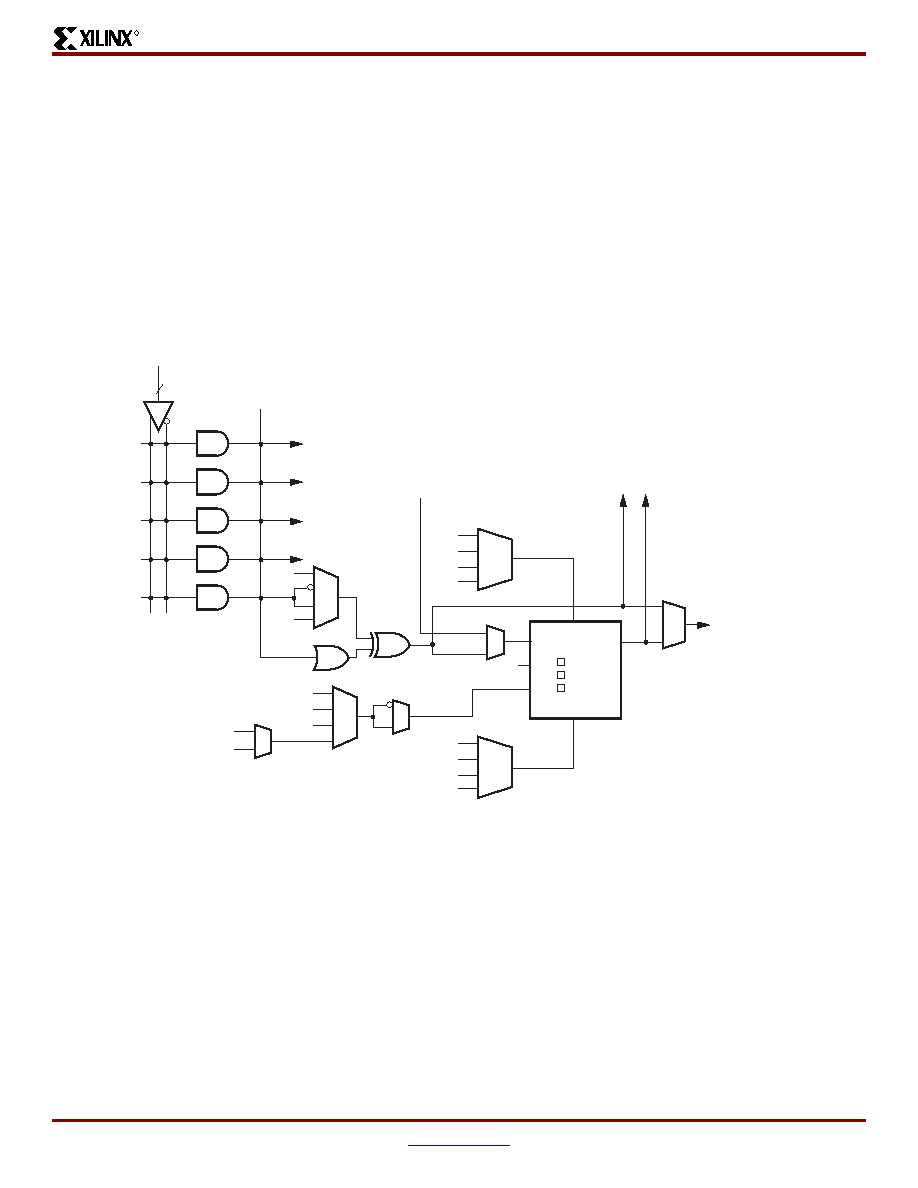

Macrocell

The CoolRunner-II CPLD macrocell is extremely efficient

and streamlined for logic creation. Users can develop sum

of product (SOP) logic expressions that comprise up to 40

inputs and span 56 product terms within a single function

block. The macrocell can further combine the SOP expres-

sion into an XOR gate with another single p-term expres-

sion. The resulting logic expression’s polarity is also

selectable. As well, the logic function can be pure combina-

torial or registered, with the storage element operating

selectably as a D or T flip-flop, or transparent latch. Avail-

able at each macrocell are independent selections of global,

function block level or local p-term derived clocks, sets,

resets, and output enables. Each macrocell flip-flop is con-

figurable for either single edge or DualEDGE clocking, pro-

viding either double data rate capability or the ability to

distribute a slower clock (thereby saving power). For single

edge clocking or latching, either clock polarity can be

selected per macrocell. CoolRunner-II CPLD macrocell

dard logic symbols are used except the trapezoidal multi-

plexers have input selection from statically programmed

configuration select lines (not shown). Xilinx application

note XAPP376 gives a detailed explanation of how logic is

created in the CoolRunner-II CPLD family.

When configured as a D-type flip-flop, each macrocell has

an optional clock enable signal permitting state hold while a

clock runs freely. Note that Control Terms (CT) are available

to be shared for key functions within the FB, and are gener-

ally used whenever the exact same logic function would be

repeatedly created at multiple macrocells. The CT product

terms are available for FB clocking (CTC), FB asynchro-

nous set (CTS), FB asynchronous reset (CTR), and FB out-

put enable (CTE).

Any macrocell flip-flop can be configured as an input regis-

ter or latch, which takes in the signal from the macrocell’s

I/O pin, and directly drives the AIM. The macrocell combina-

tional functionality is retained for use as a buried logic node

if needed. FToggle is the maximum clock frequency to which

a T flip-flop can reliably toggle.

Advanced Interconnect Matrix (AIM)

The Advanced Interconnect Matrix is a highly connected

low power rapid switch. The AIM is directed by the software

to deliver up to a set of 40 signals to each FB for the cre-

ation of logic. Results from all FB macrocells, as well as, all

pin inputs circulate back through the AIM for additional con-

nection available to all other FBs as dictated by the design

Figure 3: CoolRunner-II CPLD Macrocell

GCK0

GCK1

GCK2

CTC

PTC

DS090_03_121201

49 P-terms

To PTA, PTB, PTC of

other macrocells

CTC, CTR,

CTS, CTE

From AIM

4 P-terms

PTA

Direct Input

from

I/O Block

Feedback

to AIM

PTB

PTC

PLA OR Term

PTA

CTS

GSR

GND

VCC

R

D/T

CE

CK

FIF

Latch

DualEDGE

Q

S

40

To I/O Block

PTA

CTR

GSR

GND

相关PDF资料 |

PDF描述 |

|---|---|

| RBM12DRKH | CONN EDGECARD 24POS DIP .156 SLD |

| EGM43DTBT-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| REC3-2412SR/H1/SMD-R | CONV DC/DC 3W 24VIN 12VOUT |

| TAP334M035HSB | CAP TANT 0.33UF 35V 20% RADIAL |

| EMM06DRMS | CONN EDGECARD 12POS .156 WW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2C64A-7VQG100I | 功能描述:IC CR-II CPLD 64MCELL 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:90 系列:ispMACH® 4A 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:4.75 V ~ 5.25 V 逻辑元件/逻辑块数目:- 宏单元数:64 门数:- 输入/输出数:48 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 |

| XC2C64A-7VQG44C | 功能描述:IC CR-II CPLD 64MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:90 系列:ispMACH® 4A 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:4.75 V ~ 5.25 V 逻辑元件/逻辑块数目:- 宏单元数:64 门数:- 输入/输出数:48 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 |

| XC2C64A-7VQG44I | 功能描述:IC CR-II CPLD 64MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:90 系列:ispMACH® 4A 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:4.75 V ~ 5.25 V 逻辑元件/逻辑块数目:- 宏单元数:64 门数:- 输入/输出数:48 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 |

| XC2C64SERIES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:CoolRunner-II CPLD |

| XC2JC101 | 制造商:Schneider Electric 功能描述:LIMIT SWITCH 600VDC 10AMP XC2J +OPTIONS 制造商:SCHNEIDER ELECTRIC 功能描述:Switch Access Limit Switch |

发布紧急采购,3分钟左右您将得到回复。