参数资料

| 型号: | XC2S200E-6FG456C |

| 厂商: | Xilinx Inc |

| 文件页数: | 36/108页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 1176 CLB'S 456-FPGA |

| 标准包装: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 1176 |

| 逻辑元件/单元数: | 5292 |

| RAM 位总计: | 57344 |

| 输入/输出数: | 289 |

| 门数: | 200000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 456-BBGA |

| 供应商设备封装: | 456-FBGA |

| 其它名称: | 122-1210 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-3 (v3.0) August 9, 2013

33

Product Specification

Spartan-IIE FPGA Family: DC and Switching Characteristics

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

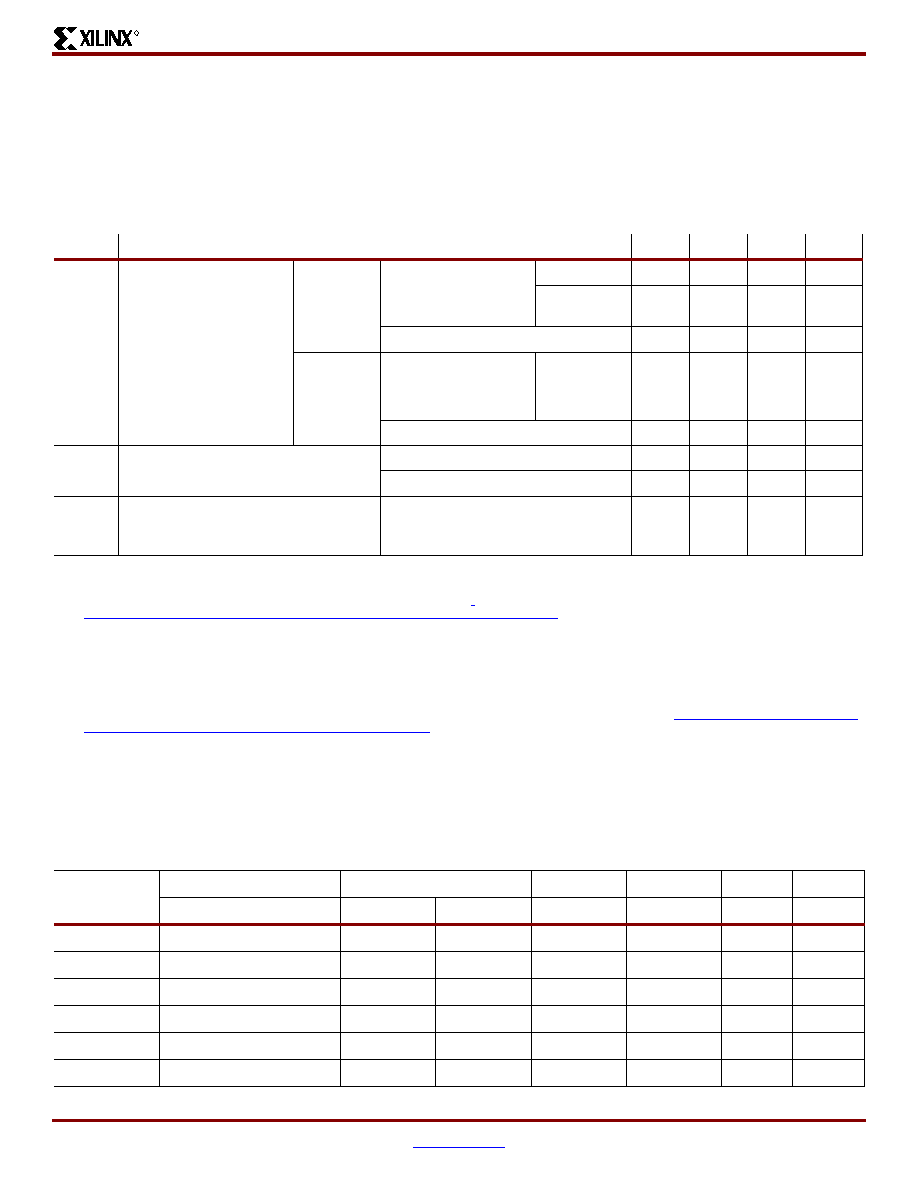

Power-On Requirements

Spartan-IIE FPGAs require that a minimum supply current

ICCPO be provided to the VCCINT lines for a successful

power-on. If more current is available, the FPGA can con-

sume more than ICCPO min., though this cannot adversely

affect reliability.

A maximum limit for ICCPO is not specified. Be careful when

using foldback/crowbar supplies and fuses. It is possible to

control the magnitude of ICCPO by limiting the supply current

available to the FPGA. A current limit below the trip level will

avoid inadvertently activating over-current protection cir-

cuits.

DC Input and Output Levels

Values for VIL and VIH are recommended input voltages.

Values for VOL and VOH are guaranteed output voltages

over the recommended operating conditions. Only selected

standards are tested. These are chosen to ensure that all

standards meet their specifications. The selected standards

are tested at minimum VCCO with the respective IOL and IOH

currents shown. Other standards are sample tested.

Symbol

Description

Min(1)

Typ

Max

Units

ICCPO

Total VCCINT supply current

required during power-on

Commercial

XC2S50E - XC2S300E

After PCN(2)

300

-

mA

Before

PCN(2)

500

-

mA

XC2S400E - XC2S600E

500

-

mA

Industrial

XC2S50E - XC2S300E

After PCN(2)

500

-

mA

Before

PCN(2)

2

-

A

XC2S400E - XC2S600E

700

-

mA

TCCPO

VCCINT(3,4) ramp time

After PCN(2)

500

-

μs

Before PCN(2)

2

-

50

ms

IHSPO

AC current per pin during power-on in

hot-swap applications when

VIN > VCCO + 0.4V; duration < 10ns

After PCN(2)

-

±60

-

μA

Notes:

1.

The ICCPO requirement applies for a brief time (commonly only a few milliseconds) when VCCINT ramps from 0 to 1.8V.

2.

Devices built after the Product Change Notice PCN 2002-05 (see

http://www.xilinx.com/support/documentation/customer_notices/pcn2002-05.pdf) have improved power-on requirements. Devices

after the PCN have a ‘T’ preceding the date code as referenced in the PCN. Note that the XC2S150E, XC2S400E, and XC2S600E

always have this mark. Devices before the PCN have an ‘S’ preceding the date code. Note that devices before the PCN are

measured with VCCINT and VCCO powering up simultaneously.

3.

The ramp time is measured from GND to 1.8V on a fully loaded board.

4.

VCCINT must not dip in the negative direction during power on.

5.

I/Os are not guaranteed to be disabled until VCCINT is applied.

6.

For more information on designing to meet the power-on specifications, refer to the application note XAPP450 "Power-On Current

Input/Output

Standard

VIL

VIH

VOL

VOH

IOL

IOH

V, Min

V, Max

V, Min

V, Max

V, Min

mA

LVTTL(1)

–0.5

0.8

2.0

3.6

0.4

2.4

24

–24

LVCMOS2

–0.5

0.7

1.7

2.7

0.4

1.9

12

–12

LVCMOS18

–0.5

35% VCCO

65% VCCO

1.95

0.4

VCCO – 0.4

8

–8

PCI, 3.3V

–0.5

30% VCCO

50% VCCO

VCCO + 0.5

10% VCCO

90% VCCO

Note (2)

GTL

–0.5

VREF – 0.05

VREF + 0.05

3.6

0.4

-

40

-

GTL+

–0.5

VREF – 0.1

VREF + 0.1

3.6

0.6

-

36

-

相关PDF资料 |

PDF描述 |

|---|---|

| 93C86CT-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

| XA6SLX16-2FTG256Q | IC FPGA SPARTAN 6 256FTGBGA |

| GMC20DTEN | CONN EDGECARD 40POS .100 EYELET |

| 93C86C-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

| GMC20DTEH | CONN EDGECARD 40POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S200E6FG456I | 制造商:XILINX 功能描述:New |

| XC2S200E-6FG456I | 制造商:Xilinx 功能描述:FPGA, 864 CLBS, 52000 GATES, 357 MHz, PBGA456 |

| XC2S200E-6FG676C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FG676I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FGG456C | 功能描述:IC SPARTAN-IIE FPGA 200K 456FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。