参数资料

| 型号: | XC3142A-3PQ100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 6/76页 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 4200GAT 100PQF |

| 产品变化通告: | XC4000XL/E, XC9500XV, XC3100A Discontinuance 12/Apr/2010 |

| 标准包装: | 66 |

| 系列: | XC3000A/L |

| LAB/CLB数: | 144 |

| RAM 位总计: | 30784 |

| 输入/输出数: | 82 |

| 门数: | 3000 |

| 电源电压: | 4.25 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-QFP(14x20) |

| 其它名称: | 122-1044 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

XC3000 Series Field Programmable Gate Arrays

7-16

November 9, 1998 (Version 3.1)

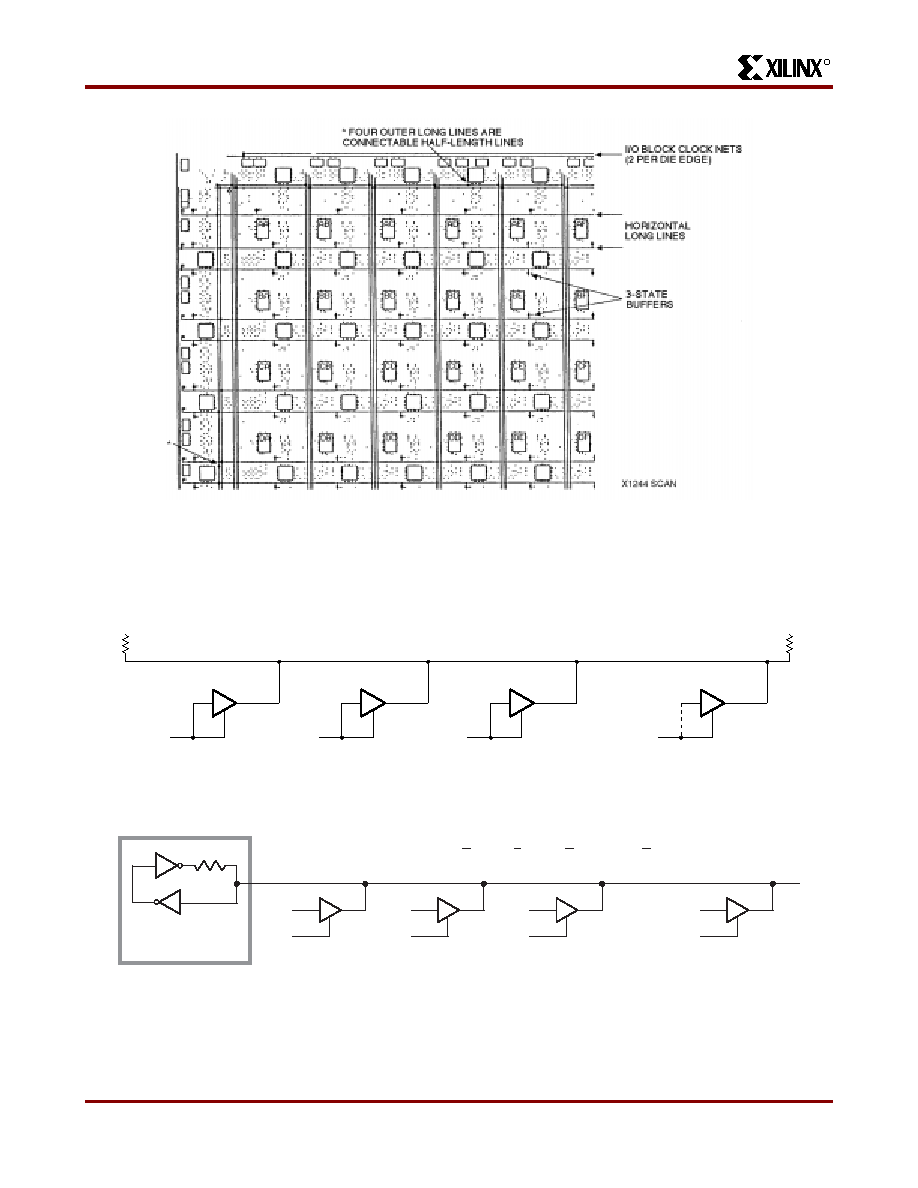

Figure 15: Programmable Interconnection of Longlines. This is provided at the edges of the routing area.

Three-state buffers allow the use of horizontal Longlines to form on-chip wired AND and multiplexed buses. The left two

non-clock vertical Longlines per column (except XC3020A) and the outer perimeter Longlines may be programmed as

connectable half-length lines.

VCC

DA

DB

DC

DN

VCC

Z = DA DB DC ... DN

X3036

(LOW)

Figure 16: 3-State Buffers Implement a Wired-AND Function. When all the buffer 3-state lines are High, (high

impedance), the pull-up resistor(s) provide the High output. The buffer inputs are driven by the control signals or a Low.

D A

A

D B

B

D C

C

D N

N

D A A

+

=D B B

+ D C C

+

D N N

Z… +

X1741A

WEAK

KEEPER CIRCUIT

Figure 17: 3-State Buffers Implement a Multiplexer. The selection is accomplished by the buffer 3-state signal.

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| AMC36DRYH-S13 | CONN EDGECARD 72POS .100 EXTEND |

| XC3130A-3PQ100C | IC LOGIC CL ARRAY 3000GAT 100PQF |

| XC3130A-3PC84C | IC LOGIC CL ARRAY 3000GAT 84PLCC |

| RCB108DHBR | CONN EDGECARD 216PS R/A .050 DIP |

| XC3120A-3PC68C | IC LOGIC CL ARRAY 2000GAT 68PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3142A-3PQ100C0262 | 制造商:Xilinx 功能描述: |

| XC3142A-3PQ100I | 制造商:Xilinx 功能描述: |

| XC3142A-3TQ144C | 制造商:Xilinx 功能描述: |

| XC3142A-3TQ144I | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3142A-3VQ100C | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。