参数资料

| 型号: | XC4013E-2BG225I |

| 厂商: | Xilinx Inc |

| 文件页数: | 57/68页 |

| 文件大小: | 0K |

| 描述: | IC FPGA I-TEMP 5V 2SPD 225-PBGA |

| 产品变化通告: | Product Discontinuation 28/Jul/2010 |

| 标准包装: | 1 |

| 系列: | XC4000E/X |

| LAB/CLB数: | 576 |

| 逻辑元件/单元数: | 1368 |

| RAM 位总计: | 18432 |

| 输入/输出数: | 192 |

| 门数: | 13000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 225-BBGA |

| 供应商设备封装: | 225-PBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页当前第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-64

May 14, 1999 (Version 1.6)

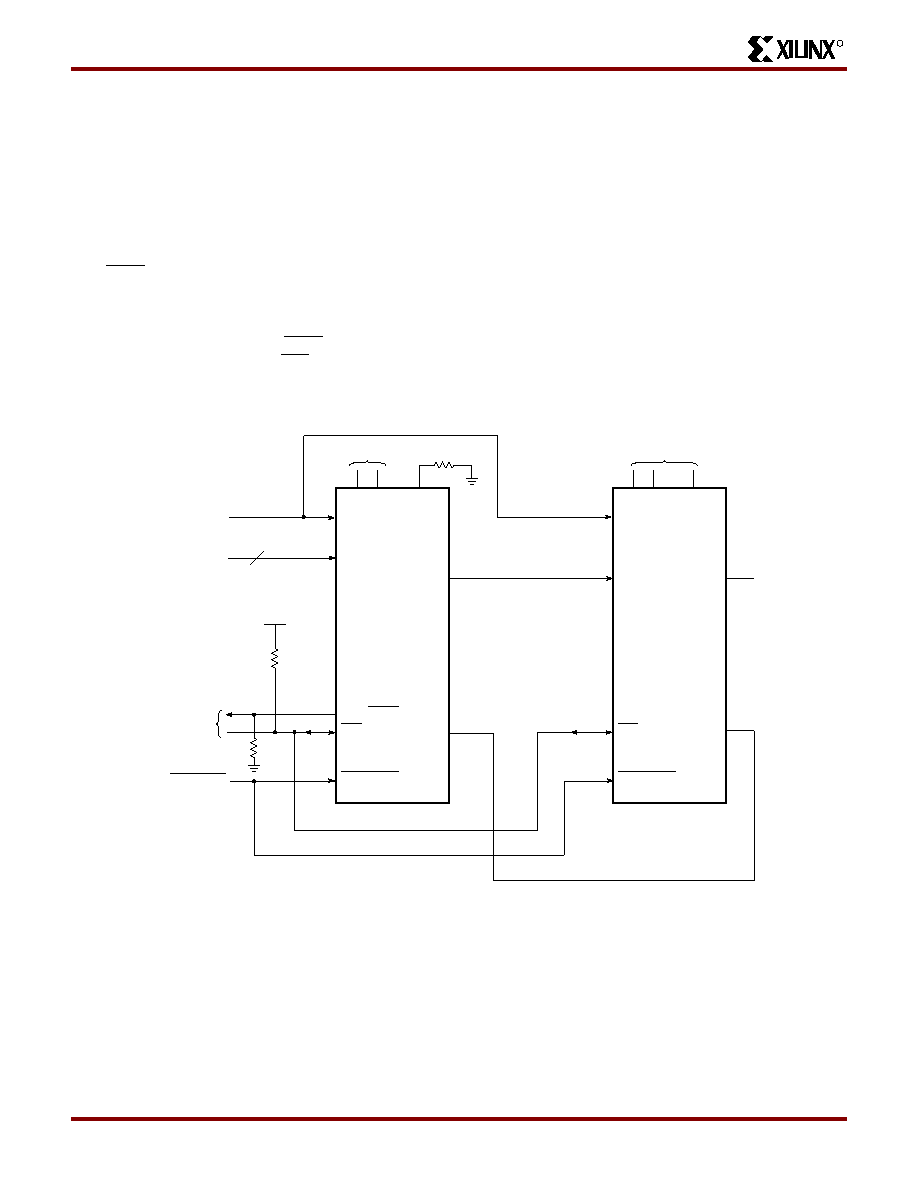

Synchronous Peripheral Mode

Synchronous Peripheral mode can also be considered

Slave Parallel mode. An external signal drives the CCLK

input(s) of the FPGA(s). The rst byte of parallel congura-

tion data must be available at the Data inputs of the lead

FPGA a short setup time before the rising CCLK edge.

Subsequent data bytes are clocked in on every eighth con-

secutive rising CCLK edge.

The same CCLK edge that accepts data, also causes the

RDY/BUSY output to go High for one CCLK period. The pin

name is a misnomer. In Synchronous Peripheral mode it is

really an ACKNOWLEDGE signal. Synchronous operation

does not require this response, but it is a meaningful signal

for test purposes. Note that RDY/BUSY is pulled High with

a high-impedance pullup prior to INIT going High.

The lead FPGA serializes the data and presents the pre-

amble data (and all data that overows the lead device) on

its DOUT pin. There is an internal delay of 1.5 CCLK peri-

ods, which means that DOUT changes on the falling CCLK

edge, and the next FPGA in the daisy chain accepts data

on the subsequent rising CCLK edge.

In order to complete the serial shift operation, 10 additional

CCLK rising edges are required after the last data byte has

been loaded, plus one more CCLK cycle for each

daisy-chained device.

Synchronous Peripheral mode is selected by a <011> on

the mode pins (M2, M1, M0).

X9027

CONTROL

SIGNALS

DATA BUS

PROGRAM

DOUT

M0 M1

M2

D0-7

INIT

DONE

PROGRAM

4.7 k

4.7 k

4.7 k

RDY/BUSY

VCC

OPTIONAL

DAISY-CHAINED

FPGAs

NOTE:

M2 can be shorted to Ground

if not used as I/O

CCLK

CLOCK

PROGRAM

DOUT

XC4000E/X

SLAVE

XC4000E/X

SYNCHRO-

NOUS

PERIPHERAL

M0 M1

N/C

8

M2

DIN

INIT

DONE

CCLK

N/C

Figure 56: Synchronous Peripheral Mode Circuit Diagram

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| XC4013E-2BG225C | IC FPGA C-TEMP 5V 2SPD 225-PBGA |

| 485897-2 | CONN PLUG 4POS HOUSING W/DETENT |

| 1-487769-3 | 015 HOUSING FFC RCPT 100CL SR |

| IDT71V546XS100PFG | IC SRAM 4MBIT 100MHZ 100TQFP |

| 487769-4 | CONN RECEPT 6 POS .100 SLIMLINE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4013E-2BG240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

| XC4013E-2BG240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

| XC4013E-2BG240M | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

| XC4013E-2CB240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

| XC4013E-2CB240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。