参数资料

| 型号: | XC5VTX240T-2FF1759C |

| 厂商: | Xilinx Inc |

| 文件页数: | 91/91页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX5TXT 240K 1759FBGA |

| 产品培训模块: | PCI Express and Virtex® -5 FPGAs |

| 标准包装: | 1 |

| 系列: | Virtex®-5 TXT |

| LAB/CLB数: | 18720 |

| 逻辑元件/单元数: | 239616 |

| RAM 位总计: | 11943936 |

| 输入/输出数: | 680 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 1759-BBGA,FCBGA |

| 供应商设备封装: | 1759-FCBGA |

| 配用: | 568-5088-ND - BOARD DEMO DAC1408D750 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页当前第91页

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

91

Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND

CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT http://www.xilinx.com/warranty.htm. THIS LIMITED

WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE

SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE

PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES

THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL

APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO

APPLICABLE LAWS AND REGULATIONS.

12/02/08

4.8

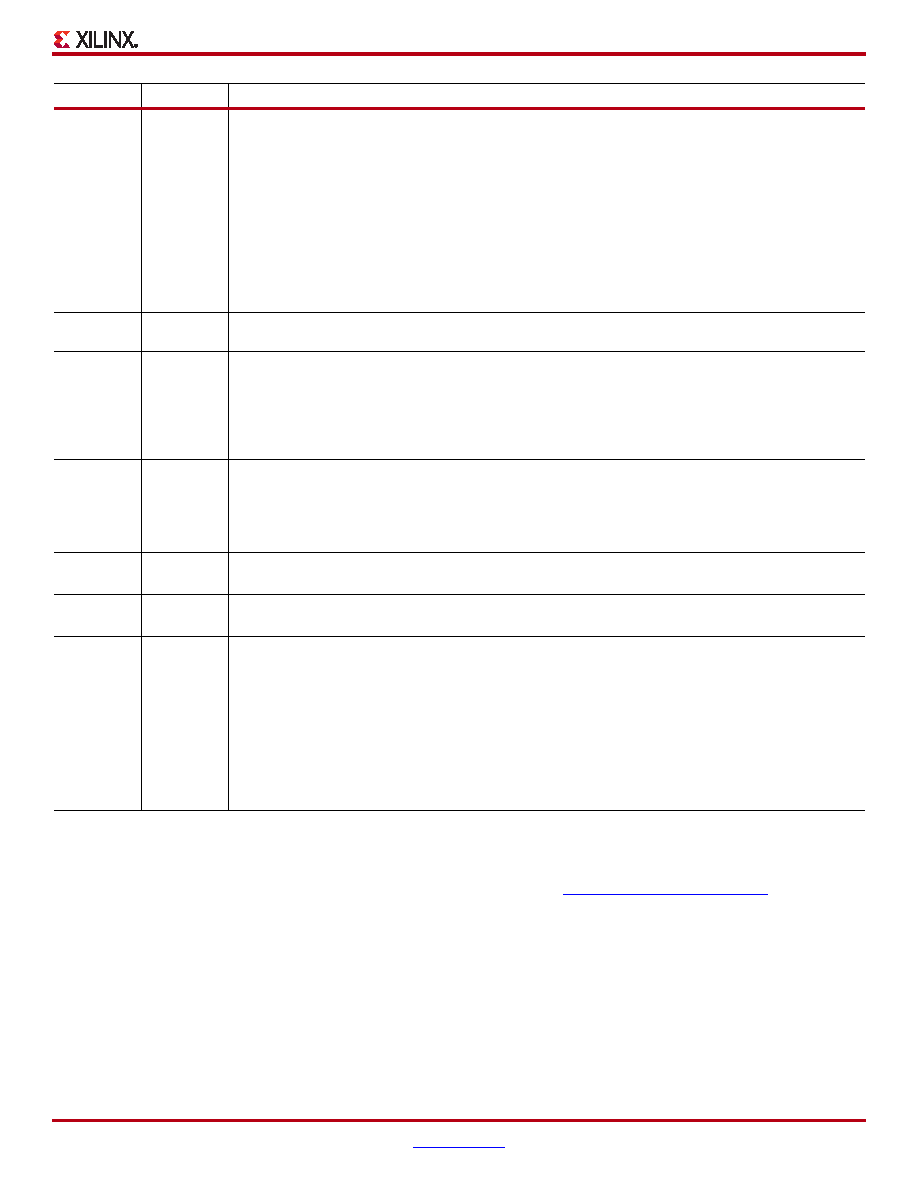

In Table 45, page 23, updated parameters with separate FXT and TXT values.

In Table 54, page 30, updated SX240T, FXT, and TXT speed grade designations.

In Table 55, page 31, updated SX240T and FXT rows.

In Table 58, page 37, added LVCMOS, 1.2V row.

In Table 80, page 60, updated note 3 with sentence about global clock tree.

12/19/08

4.9

Updated Table 5, page 6 with power-on current values for XC5VSX240T, XC5VTX150T, XC5VTX240T,

XC5VFX100T, and XC5VFX200T devices.

01/14/09

4.10

In Table 1, page 1, changed note 2 to refer to UG112 for soldering guidelines.

In Table 54, page 30, moved speed grades for the XC5VTX150T and XC5VTX240T devices to

Production.

In Table 55, page 31, added the ISE software version for the XC5VTX150T and XC5VTX240T devices.

In Table 80, page 60, moved the reference to the duty cycle distortion note to apply to both

TDUTY_CYC_DLL and TDUTY_CYC_FX.

02/06/09

5.0

Changed document classification from Advance Product Specification to Product Specification.

In Table 5, page 6, removed the Max columns and added note 2 about calculating the maximum startup

current.

04/01/09

5.1

06/25/09

5.2

In Table 2, page 2, added note 6.

05/05/10

5.3

added table note 2 about RXPPMTOL.

In Table 42, changed the minimum PLL frequency (FGPLLMIN) to 1.48 GHz for all three speed grades. In

removed “2 byte or 4 byte interface” from the Conditions column for TRX and TTX. In Table 47, added table

note 2 about RXPPMTOL.

Date

Version

Revision

相关PDF资料 |

PDF描述 |

|---|---|

| XC6VHX565T-1FFG1923I | IC FPGA VIRTEX 1924FCBGA |

| XC5VLX330-1FFG1760C | IC FPGA VIRTEX-5 330K 1760FBGA |

| AYM43DTBH | CONN EDGECARD 86POS R/A .156 SLD |

| IDT71V016SA20BFI | IC SRAM 1MBIT 20NS 48FBGA |

| ASM43DTBH | CONN EDGECARD 86POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5VTX240T-2FF1759CES | 功能描述:IC FPGA VIRTEX5TX 240K 1759FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 TXT 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XC5VTX240T-2FF1759I | 功能描述:IC FPGA VIRTEX5TXT 240K 1759FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 TXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VTX240T-2FFG1759C | 功能描述:IC FPGA VIRTEX5TXT 240K 1759FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 TXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VTX240T-2FFG1759CES | 功能描述:IC FPGA VIRTEX5TX 240K 1759FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 TXT 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XC5VTX240T-2FFG1759I | 功能描述:IC FPGA VIRTEX5TXT 240K 1759FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 TXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。