- 您现在的位置:买卖IC网 > PDF目录19664 > XCR3384XL-12FT256I (Xilinx Inc)IC CPLD 3.3V ZERO PWR 256-BGA PDF资料下载

参数资料

| 型号: | XCR3384XL-12FT256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 7/12页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 3.3V ZERO PWR 256-BGA |

| 标准包装: | 90 |

| 系列: | CoolRunner XPLA3 |

| 可编程类型: | 系统内可编程(最少 1K 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 10.8ns |

| 电压电源 - 内部: | 2.7 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 24 |

| 宏单元数: | 384 |

| 门数: | 9000 |

| 输入/输出数: | 212 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

| 包装: | 托盘 |

| 其它名称: | XCR3384XL12FT256I |

CoolRunner XPLA3 CPLD

4

DS012 (v2.5) May 26, 2009

Product Specification

R

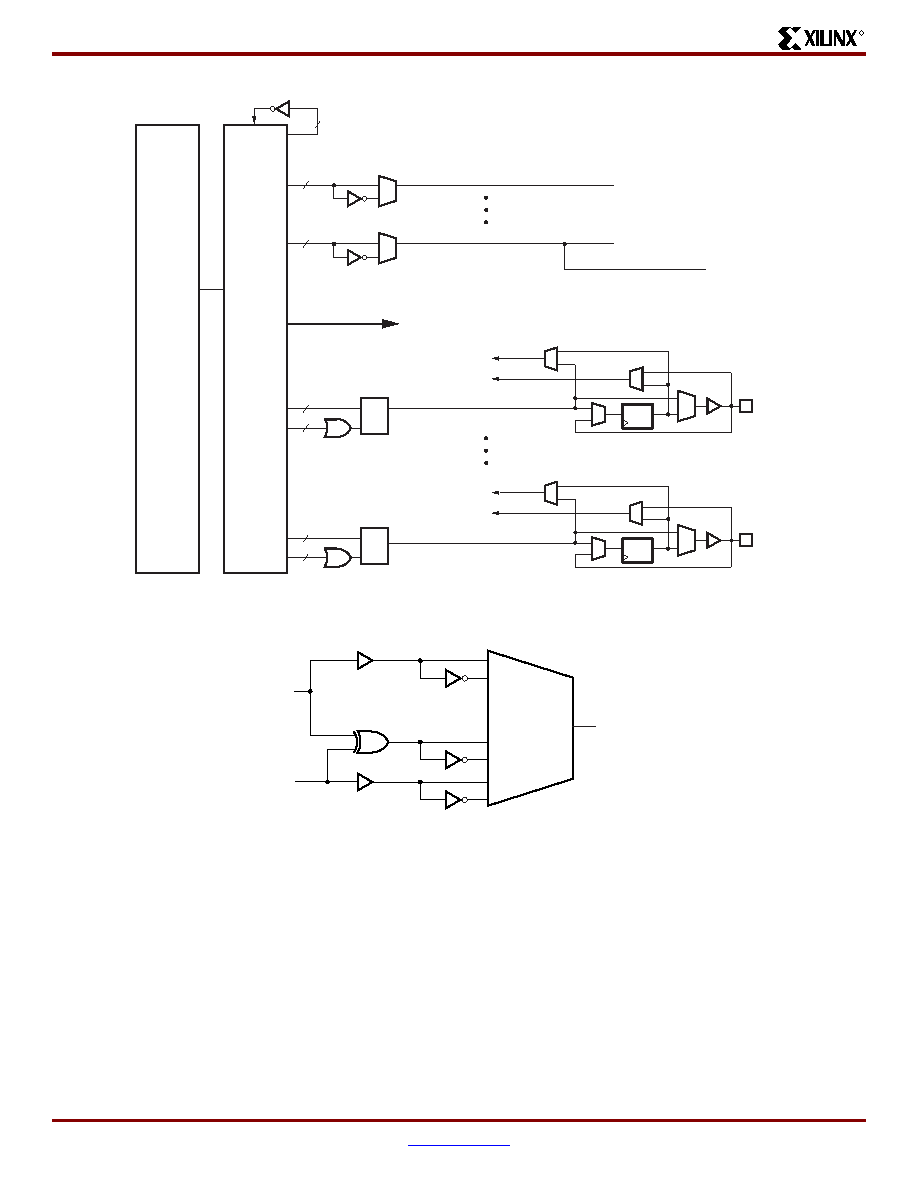

Macrocell Architecture

Figure 5 shows the architecture of the macrocell used in the

CoolRunner XPLA3 CPLD. Any macrocell can be reset or

preset on power-up. Each macrocell register can be config-

ured as a D-, T-, or Latch-type flip-flop, or bypassed if the

macrocell is required as a combinatorial logic function.

Each of these flip-flops can be clocked from any one of eight

sources or their complements. There are two global syn-

chronous clocks that are selected from the four external

clock pins. There is one universal clock signal. The clock

input signals CT[4:7] (Local Control Terms) can be individu-

ally configured as either a PRODUCT term or SUM term

equation created from the 40 signals available inside the

function block.

There are two muxed paths to the ZIA. One mux selects

from either the output of the VFM or the output of the regis-

ter. The other mux selects from the output of the register or

from the I/O pad of the macrocell. When the I/O pin is used

as an output, the output buffer is enabled, and the macrocell

feedback path can be used to feed back the logic imple-

mented in the macrocell. When an I/O pin is used as an

input, the output buffer is 3-stated and the input signal is fed

into the ZIA via the I/O feedback path. The logic imple-

Figure 3: Xilinx CoolRunner XPLA3 Function Block Architecture

Figure 4: Variable Function Multiplexer

Foldback NAND

(PT[8:15])

(PT[0:47])

(PT0)

(PT7)

(PT[32:47])

(PT16)

(PT[0:47])

(PT31)

To Local Control Term (LCT0)

To Universal Control Term (UCT) Mux

To Local Control Term (LCT7)

P-term Clocks

8

Product

Term

Array

40 x 48

ZIA

40

VFM

Macrocell 1

D

Q

I/O1

ZIA

1

48

D

Q

ZIA

I/O16

VFM

Macrocell 16

1

48

DS012_02_101200

From PLA OR Term

To Combinatorial Path

and Register Input

From P-term

DS012_03_121699

相关PDF资料 |

PDF描述 |

|---|---|

| EEM08DRUS | CONN EDGECARD 16POS DIP .156 SLD |

| XCR3384XL-10FG324C | IC CPLD 3.3V ZERO PWR 324-FBGA |

| EEC07DRYN-S13 | CONN EDGECARD 14POS .100 EXTEND |

| MCP9843-BE/ST | IC TEMP SENSOR DGTL 8-TSSOP |

| EEC07DRYH-S13 | CONN EDGECARD 14POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCR3384XL-12FTG256C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ COMM 0.35U - Trays |

| XCR3384XL-12FTG256I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ IND 0.35UM - Trays |

| XCR3384XL-12PQ208C | 功能描述:IC CPLD 3.3V ZERO PWR 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| XCR3384XL-12PQ208I | 功能描述:IC CPLD 3.3V ZERO PWR 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| XCR3384XL-12PQG208C | 制造商:Xilinx 功能描述:XLXXCR3384XL-12PQG208C XPLA3 384 MACROCE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ COMM 0.35U - Trays |

发布紧急采购,3分钟左右您将得到回复。