- 您现在的位置:买卖IC网 > PDF目录19664 > XCR3384XL-12FT256I (Xilinx Inc)IC CPLD 3.3V ZERO PWR 256-BGA PDF资料下载

参数资料

| 型号: | XCR3384XL-12FT256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 8/12页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 3.3V ZERO PWR 256-BGA |

| 标准包装: | 90 |

| 系列: | CoolRunner XPLA3 |

| 可编程类型: | 系统内可编程(最少 1K 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 10.8ns |

| 电压电源 - 内部: | 2.7 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 24 |

| 宏单元数: | 384 |

| 门数: | 9000 |

| 输入/输出数: | 212 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

| 包装: | 托盘 |

| 其它名称: | XCR3384XL12FT256I |

CoolRunner XPLA3 CPLD

DS012 (v2.5) May 26, 2009

Product Specification

R

mented in the buried macrocell can be fed back to the ZIA

via the macrocell feedback path.

If a macrocell pin is configured as a registered input, there is

a direct path to the register to provide a fast input setup

time. If the macrocell is configured as a latch, the register

clock input functions as the latch enable, with the latch

transparent when this signal is High. The hardwired clock

enable is non-functional when the macrocell is configured

as a latch.

I/O Cell

The OE (Output Enable) multiplexer has eight possible

modes (Figure 6). When the I/O Cell is configured as an

input (or 3-stated output), a half latch feature exists. This

half latch pulls the input High (through a weak pull-up) if the

input should float and cross the threshold. This protects the

input from staying in the linear region and causing an

increased amount of power consumption. This same weak

pull-up can be enabled in software such that it is always on

when the I/O Cell is configured as an input. This weak pull

up is automatically turned on when a pin is unused by the

design.

The I/O Cell is 5V tolerant when the device is powered.

Each output has independent slew rate control (fast or slow)

which assists in reducing EMI emissions.

See individual device data sheets for 3.3V PCI electrical

specification compatibility.

Note that an I/O macrocell used as buried logic that does

not have the I/O pin used for input is considered to be

unused, and the weak pull-up resistors will be turned on. It

is recommended that any unused I/O pins on the CoolRun-

ner XPLA3 family of CPLDs be left unconnected. Dedicated

input pins (CLKx/INx) do not have on-chip weak pull-up

resistors; therefore unused dedicated input pins must have

external termination. As with all CMOS devices, do not

allow inputs to float.

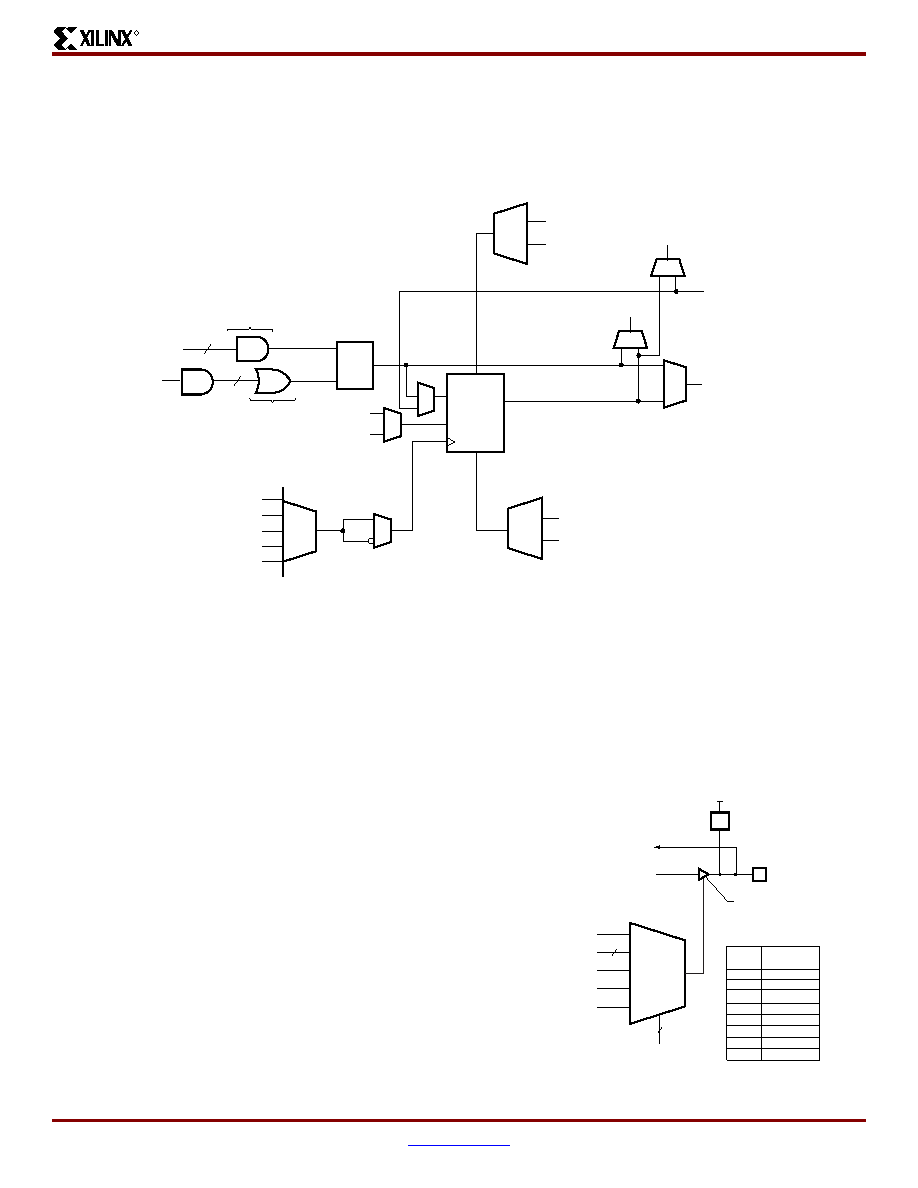

Figure 5: XPLA3 Macrocell Architecture

Global CLK

Universal CLK

P-term CLK

CT [4:7]

ds012_05_122299

Universal PST

CT [0:5]

Universal RST

CT [0:5]

To ZIA

To I/O

PAD

Note: Global CLK signals come from pins.

To ZIA

VFM

RST

PST

D/T/L

CLKEn

Q

CT4

P-term

48

PLA OR Term

From PT Array

1

Figure 6: I/O Cell

GND (Weak P.U.)

VCC

Universal OE

CT

GND

OE [2:0]

To Macrocell / ZIA

From Macrocell

I/O Pin

WP

Slew

Control

OE

Decode

0

1

2

3

4

5

6

7

I/O Pin

State

3-State

Function CT0

Function CT1

Function CT2

Function CT6

Universal OE

Enable

Weak P.U.

ds012_06_121699

Weak Pull-up

OE = 7

VCC

3

4

相关PDF资料 |

PDF描述 |

|---|---|

| EEM08DRUS | CONN EDGECARD 16POS DIP .156 SLD |

| XCR3384XL-10FG324C | IC CPLD 3.3V ZERO PWR 324-FBGA |

| EEC07DRYN-S13 | CONN EDGECARD 14POS .100 EXTEND |

| MCP9843-BE/ST | IC TEMP SENSOR DGTL 8-TSSOP |

| EEC07DRYH-S13 | CONN EDGECARD 14POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCR3384XL-12FTG256C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ COMM 0.35U - Trays |

| XCR3384XL-12FTG256I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ IND 0.35UM - Trays |

| XCR3384XL-12PQ208C | 功能描述:IC CPLD 3.3V ZERO PWR 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| XCR3384XL-12PQ208I | 功能描述:IC CPLD 3.3V ZERO PWR 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| XCR3384XL-12PQG208C | 制造商:Xilinx 功能描述:XLXXCR3384XL-12PQG208C XPLA3 384 MACROCE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ COMM 0.35U - Trays |

发布紧急采购,3分钟左右您将得到回复。