参数资料

| 型号: | XCS05XL-5VQ100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 41/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 3.3V C-TEMP 100-VQFP |

| 产品变化通告: | Product Discontinuation 26/Oct/2011 |

| 标准包装: | 90 |

| 系列: | Spartan®-XL |

| LAB/CLB数: | 100 |

| 逻辑元件/单元数: | 238 |

| RAM 位总计: | 3200 |

| 输入/输出数: | 77 |

| 门数: | 5000 |

| 电源电压: | 3 V ~ 3.6 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-VQFP(14x14) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

46

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

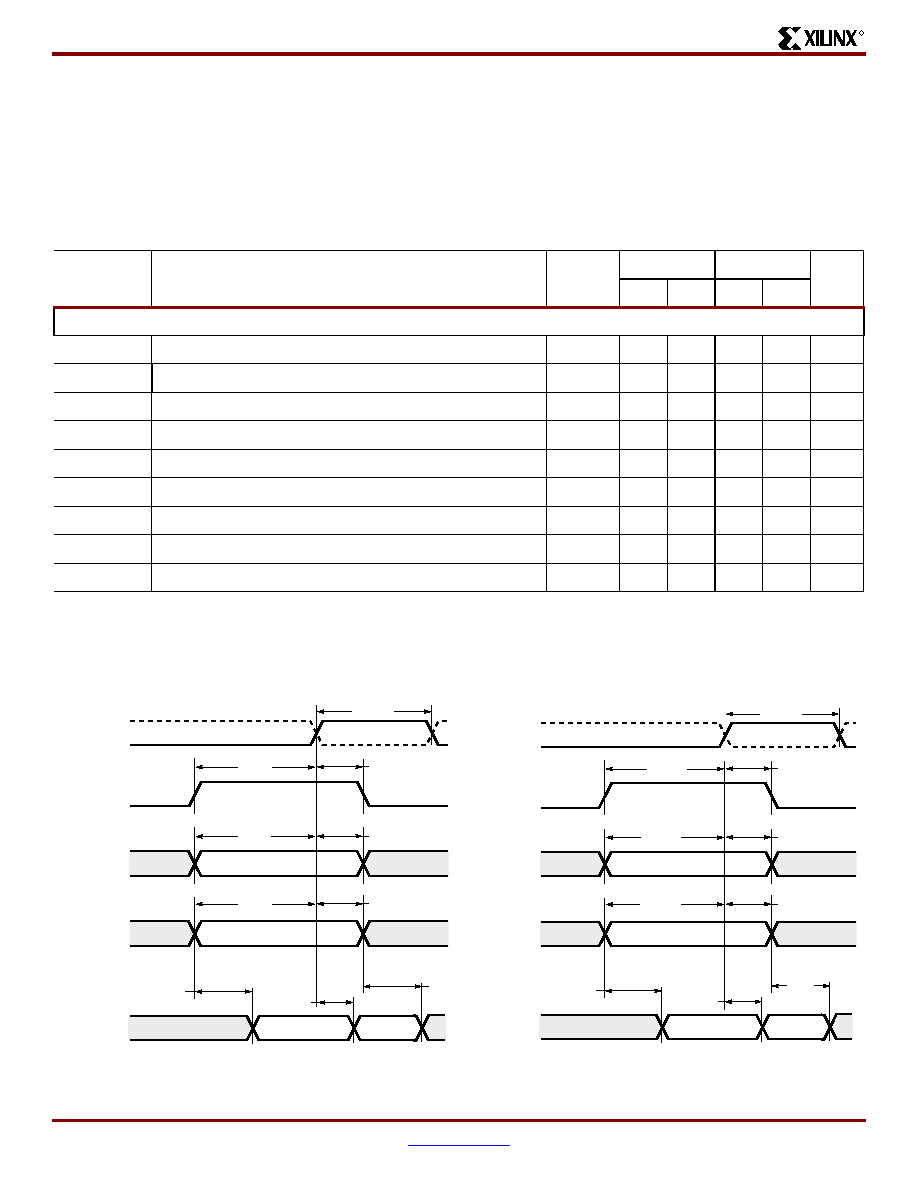

Spartan Family CLB RAM Synchronous (Edge-Triggered) Write Operation Guidelines

(continued)

All devices are 100% functionally tested. Internal timing

parameters are derived from measuring internal test pat-

terns. Listed below are representative values. For more

specific, more precise, and worst-case guaranteed data,

use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to

the simulation netlist. All timing parameters assume

worst-case operating conditions (supply voltage and junc-

tion temperature). Values apply to all Spartan devices and

are expressed in nanoseconds unless otherwise noted.

Spartan Family CLB RAM Synchronous (Edge-Triggered) Write Timing

Dual-Port RAM Synchronous (Edge-Triggered) Write Operation Characteristics

Symbol

Dual Port RAM

Size(1)

-4

-3

Units

Min

Max

Min

Max

Write Operation

TWCDS

Address write cycle time (clock K period)

16x1

8.0

-

11.6

-

ns

TWPDS

Clock K pulse width (active edge)

16x1

4.0

-

5.8

-

ns

TASDS

Address setup time before clock K

16x1

1.5

-

2.1

-

ns

TAHDS

Address hold time after clock K

16x1

0

-

0

-

ns

TDSDS

DIN setup time before clock K

16x1

1.5

-

1.6

-

ns

TDHDS

DIN hold time after clock K

16x1

0

-

0

-

ns

TWSDS

WE setup time before clock K

16x1

1.5

-

1.6

-

ns

TWHDS

WE hold time after clock K

16x1

0

-

0

-

ns

TWODS

Data valid after clock K

16x1

-

6.5

-

7.0

ns

Notes:

1.

Read Operation timing for 16 x 1 dual-port RAM option is identical to 16 x 2 single-port RAM timing

Single Port

Dual Port

WCLK (K)

WE

ADDRESS

DATA IN

DATA OUT

OLD

NEW

TDSS

TDHS

TASS

TAHS

TWSS

TWPS

TWHS

TWSDS

TWHDS

TWOS

TILO

DS060_34_011300

WCLK (K)

WE

ADDRESS

DATA IN

DATA OUT

OLD

NEW

TDSDS

TDHDS

TASDS

TAHDS

TWPDS

TWODS

TILO

相关PDF资料 |

PDF描述 |

|---|---|

| XCS05XL-5PC84C | IC FPGA 3.3V C-TEMP 84-PLCC |

| 65801-032LF | CLINCHER RECEPTACLE ASSY TIN |

| IDT71V321S55TF8 | IC SRAM 16KBIT 55NS 64STQFP |

| IDT71321SA55TF8 | IC SRAM 16KBIT 55NS 64STQFP |

| IDT7140SA35PF8 | IC SRAM 8KBIT 35NS 64TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS05XL-5VQ100I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS05XL-5VQ144C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ144I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ208C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-5VQ208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。