参数资料

| 型号: | XCS20-3VQ100C |

| 厂商: | Xilinx Inc |

| 文件页数: | 58/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V C-TEMP 100-VQFP |

| 产品变化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 标准包装: | 90 |

| 系列: | Spartan® |

| LAB/CLB数: | 400 |

| 逻辑元件/单元数: | 950 |

| RAM 位总计: | 12800 |

| 输入/输出数: | 77 |

| 门数: | 20000 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-VQFP(14x14) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

61

Product Specification

R

Product Obsolete/Under Obsolescence

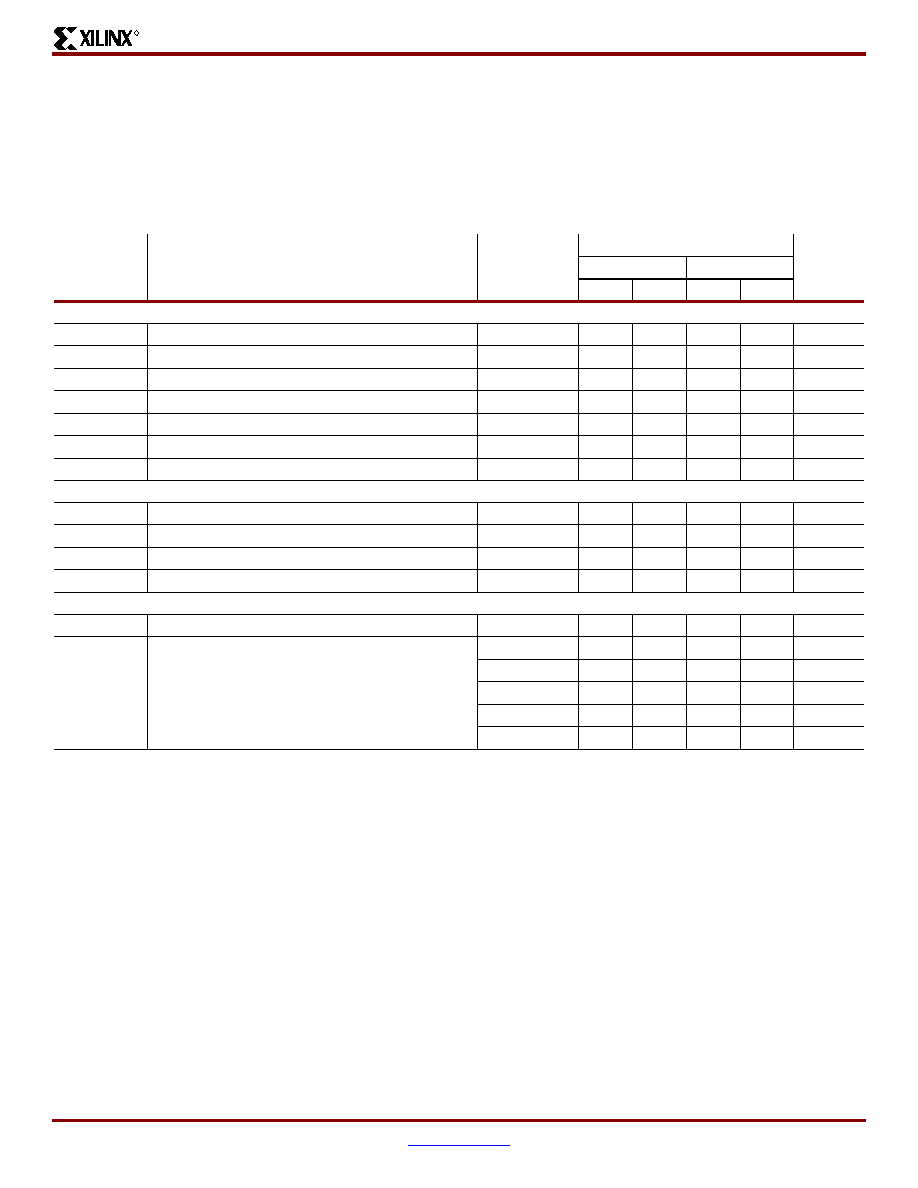

Spartan-XL Family IOB Output Switching Characteristic Guidelines

All devices are 100% functionally tested. Internal timing

parameters are derived from measuring internal test pat-

terns. Listed below are representative values. For more

specific, more precise, and worst-case guaranteed data,

use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to

the simulation netlist. These path delays, provided as a

guideline, have been extracted from the static timing ana-

lyzer report. All timing parameters assume worst-case oper-

ating conditions (supply voltage and junction temperature).

Values are expressed in nanoseconds unless otherwise

noted.

Symbol

Description

Device

Speed Grade

Units

-5

-4

Min

Max

Min

Max

Propagation Delays

TOKPOF

Clock (OK) to Pad, fast

All devices

-

3.2

-

3.7

ns

TOPF

Output (O) to Pad, fast

All devices

-

2.5

-

2.9

ns

TTSHZ

3-state to Pad High-Z (slew-rate independent)

All devices

-

2.8

-

3.3

ns

TTSONF

3-state to Pad active and valid, fast

All devices

-

2.6

-

3.0

ns

TOFPF

Output (O) to Pad via Output MUX, fast

All devices

-

3.7

-

4.4

ns

TOKFPF

Select (OK) to Pad via Output MUX, fast

All devices

-

3.3

-

3.9

ns

TSLOW

For Output SLOW option add

All devices

-

1.5

-

1.7

ns

Setup and Hold Times

TOOK

Output (O) to clock (OK) setup time

All devices

0.5

-

0.5

-

ns

TOKO

Output (O) to clock (OK) hold time

All devices

0.0

-

0.0

-

ns

TECOK

Clock Enable (EC) to clock (OK) setup time

All devices

0.0

-

0.0

-

ns

TOKEC

Clock Enable (EC) to clock (OK) hold time

All devices

0.1

-

0.2

-

ns

Global Set/Reset

TMRW

Minimum GSR pulse width

All devices

10.5

-

11.5

-

ns

TRPO

Delay from GSR input to any Pad

XCS05XL

-

11.9

-

14.0

ns

XCS10XL

-

12.4

-

14.5

ns

XCS20XL

-

12.9

-

15.0

ns

XCS30XL

-

13.9

-

16.0

ns

XCS40XL

-

14.9

-

17.0

ns

Notes:

1.

Output timing is measured at ~50% VCC threshold, with 50 pF external capacitive loads including test fixture. Slew-rate limited output

rise/fall times are approximately two times longer than fast output rise/fall times.

2.

Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up

(default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

相关PDF资料 |

PDF描述 |

|---|---|

| XCS20-3TQ144I | IC FPGA 5V I-TEMP 144-TQFP |

| IDT70V05S15J | IC SRAM 64KBIT 15NS 68PLCC |

| MPC8378VRALG | MPU POWERQUICC II PRO 689-PBGA |

| MPC8377VRALG | MPU POWERQUICC II PRO 689-PBGA |

| MPC866PCZP100A | IC MPU POWERQUICC 100MHZ 357PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS20-3VQ100I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ144C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ144I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ208C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。