- 您现在的位置:买卖IC网 > PDF目录300152 > XCS20XL-3BG208I (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XCS20XL-3BG208I |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴达和Spartan - xL的家庭现场可编程门阵列 |

| 文件页数: | 38/82页 |

| 文件大小: | 863K |

| 代理商: | XCS20XL-3BG208I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

Spartan and Spartan-XL Families Field Programmable Gate Arrays

DS060 (v1.6) September 19, 2001

Product Specification

1-800-255-7778

R

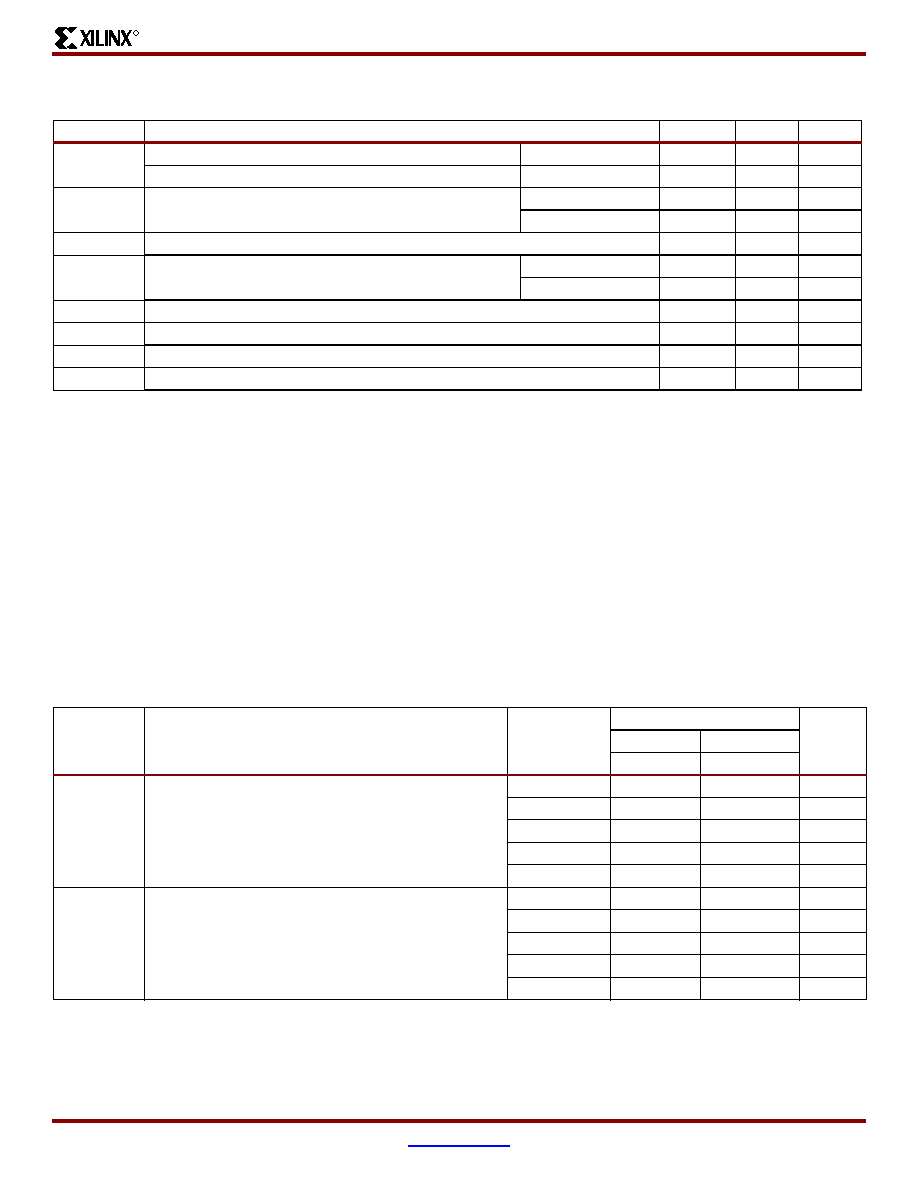

Spartan DC Characteristics Over Operating Conditions

Spartan Global Buffer Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing

methods specified by MIL-M-38510/605. All devices are

100% functionally tested. Internal timing parameters are

derived from measuring internal test patterns. Listed below

are representative values where one global clock input

drives one vertical clock line in each accessible column, and

where all accessible IOB and CLB flip-flops are clocked by

the global clock net.

When fewer vertical clock lines are connected, the clock dis-

tribution is faster; when multiple clock lines per column are

driven from the same global clock, the delay is longer. For

more specific, more precise, and worst-case guaranteed

data, reflecting the actual routing structure, use the values

provided by the static timing analyzer (TRCE in the Xilinx

Development System) and back-annotated to the simulation

netlist. These path delays, provided as a guideline, have

been extracted from the static timing analyzer report. All

timing parameters assume worst-case operating conditions

(supply voltage and junction temperature).

Symbol

Description

Min

Max

Units

VOH

High-level output voltage @ IOH = –4.0 mA, VCC min

TTL outputs

2.4

-

V

High-level output voltage @ IOH = –1.0 mA, VCC min

CMOS outputs

VCC – 0.5

-

V

VOL

Low-level output voltage @ IOL = 12.0 mA, VCC min(1)

TTL outputs

-

0.4

V

CMOS outputs

-

0.4

V

VDR

Data retention supply voltage (below which configuration data may be lost)

3.0

-

V

ICCO

Quiescent FPGA supply current(2)

Commercial

-

3.0

mA

Industrial

-

6.0

mA

IL

Input or output leakage current

–10

+10

A

CIN

Input capacitance (sample tested)

-

10

pF

IRPU

Pad pull-up (when selected) @ VIN = 0V (sample tested)

0.02

0.25

mA

IRPD

Pad pull-down (when selected) @ VIN = 5V (sample tested)

0.02

-

mA

Notes:

1.

With 50% of the outputs simultaneously sinking 12 mA, up to a maximum of 64 pins.

2.

With no output current loads, no active input pull-up resistors, all package pins at VCC or GND, and the FPGA configured with a Tie

option.

Symbol

Description

Device

Speed Grade

Units

-4

-3

Max

TPG

From pad through Primary buffer, to any clock K

XCS05

2.0

4.0

ns

XCS10

2.4

4.3

ns

XCS20

2.8

5.4

ns

XCS30

3.2

5.8

ns

XCS40

3.5

6.4

ns

TSG

From pad through Secondary buffer, to any clock K

XCS05

2.5

4.4

ns

XCS10

2.9

4.7

ns

XCS20

3.3

5.8

ns

XCS30

3.6

6.2

ns

XCS40

3.9

6.7

ns

相关PDF资料 |

PDF描述 |

|---|---|

| XCS20XL-3BG240C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG256C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG256I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG280C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS20XL-3BG240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS20XL-3BG280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。