- 您现在的位置:买卖IC网 > PDF目录300152 > XCS20XL-3BG280C (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XCS20XL-3BG280C |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴达和Spartan - xL的家庭现场可编程门阵列 |

| 文件页数: | 26/82页 |

| 文件大小: | 863K |

| 代理商: | XCS20XL-3BG280C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

Spartan and Spartan-XL Families Field Programmable Gate Arrays

32

DS060 (v1.6) September 19, 2001

1-800-255-7778

Product Specification

R

Legend:

A selection of CRC or non-CRC error checking is allowed by

the bitstream generation software. The Spartan-XL Express

mode

only

supports

non-CRC

error

checking.

The

non-CRC

error

checking

tests

for

a

designated

end-of-frame field for each frame. For CRC error checking,

the software calculates a running CRC and inserts a unique

four-bit partial check at the end of each frame. The 11-bit

CRC check of the last frame of an FPGA includes the last

seven data bits.

Detection of an error results in the suspension of data load-

ing before DONE goes High, and the pulling down of the

INIT pin. In Master serial mode, CCLK continues to operate

externally. The user must detect INIT and initialize a new

configuration by pulsing the PROGRAM pin Low or cycling

VCC.

Cyclic Redundancy Check (CRC) for Configura-

tion and Readback

The Cyclic Redundancy Check is a method of error detec-

tion in data transmission applications. Generally, the trans-

mitting system performs a calculation on the serial

bitstream. The result of this calculation is tagged onto the

data stream as additional check bits. The receiving system

performs an identical calculation on the bitstream and com-

pares the result with the received checksum.

Each data frame of the configuration bitstream has four

error bits at the end, as shown in Table 16. If a frame data

error is detected during the loading of the FPGA, the config-

uration process with a potentially corrupted bitstream is ter-

minated. The FPGA pulls the INIT pin Low and goes into a

Wait state.

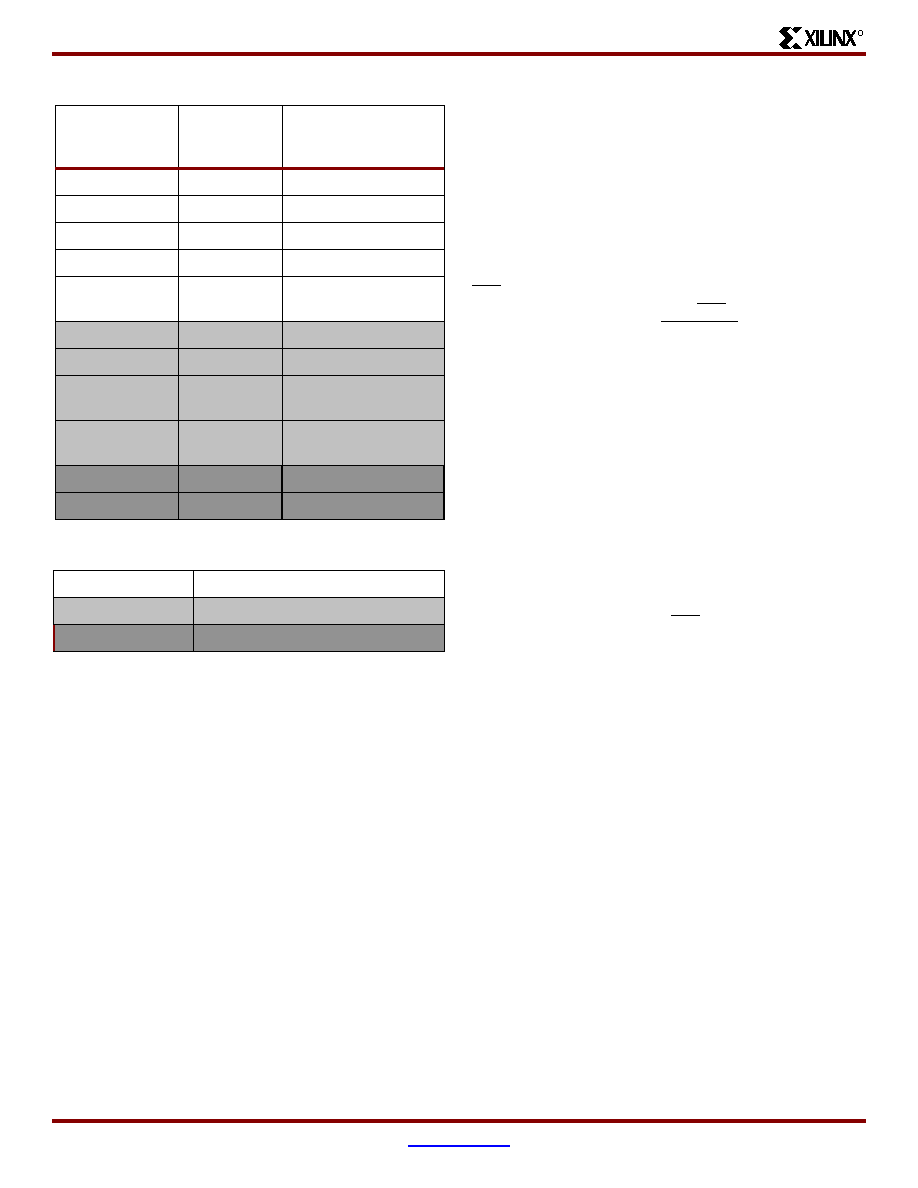

Table 16: Spartan/XL Data Stream Formats

Data Type

Serial Modes

(D0...)

Express Mode

(D0-D7)

(Spartan-XL only)

Fill Byte

11111111b

FFFFh

Preamble Code

0010b

11110010b

Length Count

COUNT[23:0]

COUNT[23:0](1)

Fill Bits

1111b

-

Field Check

Code

-

11010010b

Start Field

0b

11111110b(2)

Data Frame

DATA[n–1:0]

CRC or Constant

Field Check

xxxx (CRC)

or 0110b

11010010b

Extend Write

Cycle

-

FFD2FFFFFFh

Postamble

01111111b

-

Start-Up Bytes(3)

FFh

FFFFFFFFFFFFFFh

Unshaded

Once per bitstream

Light

Once per data frame

Dark

Once per device

Notes:

1.

Not used by configuration logic.

2.

11111111b for XCS40XL only.

3.

Development system may add more start-up bytes.

相关PDF资料 |

PDF描述 |

|---|---|

| XCS20XL-3BG280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG84I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3CS100C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3CS100I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3CS144C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS20XL-3BG280I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG84C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3BG84I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3CS100C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-3CS100I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。