- 您现在的位置:买卖IC网 > PDF目录300161 > XCV405E-6FG676I (XILINX INC) Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XCV405E-6FG676I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| 中文描述: | FPGA, 2400 CLBS, 129600 GATES, 357 MHz, PBGA676 |

| 封装: | PLASTIC, FBGA-676 |

| 文件页数: | 3/20页 |

| 文件大小: | 191K |

| 代理商: | XCV405E-6FG676I |

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-3 (v2.3.2) March 14, 2003

Module 3 of 4

1-800-255-7778

11

R

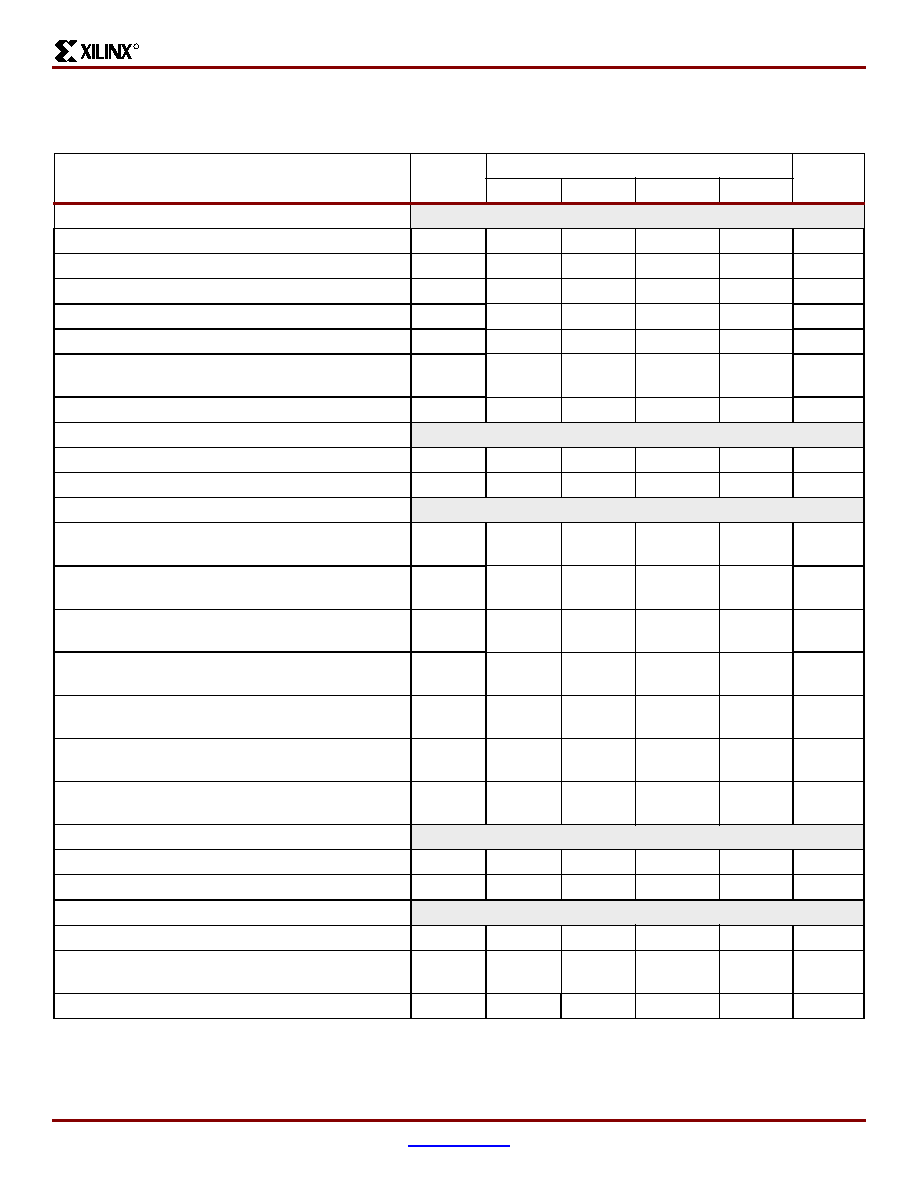

CLB Switching Characteristics

Delays originating at F/G inputs vary slightly according to the input used, see Figure 2. The values listed below are

worst-case. Precise values are provided by the timing analyzer.

Description(1)

Symbol

Speed Grade

Units

Min

-8

-7

-6

Combinatorial Delays

4-input function: F/G inputs to X/Y outputs

TILO

0.19

0.40

0.42

0.47

ns, max

5-input function: F/G inputs to F5 output

TIF5

0.36

0.76

0.8

0.9

ns, max

5-input function: F/G inputs to X output

TIF5X

0.35

0.74

0.8

0.9

ns, max

6-input function: F/G inputs to Y output via F6 MUX

TIF6Y

0.35

0.74

0.9

1.0

ns, max

6-input function: F5IN input to Y output

TF5INY

0.04

0.11

0.20

0.22

ns, max

Incremental delay routing through transparent latch

to XQ/YQ outputs

TIFNCTL

0.27

0.63

0.7

0.8

ns, max

BY input to YB output

TBYYB

0.19

0.38

0.46

0.51

ns, max

Sequential Delays

FF Clock CLK to XQ/YQ outputs

TCKO

0.34

0.78

0.9

1.0

ns, max

Latch Clock CLK to XQ/YQ outputs

TCKLO

0.40

0.77

0.9

1.0

ns, max

Setup and Hold Times before/after Clock CLK

4-input function: F/G Inputs

TICK /

TCKI

0.39 / 0

0.9 / 0

1.0 / 0

1.1 / 0

ns, min

5-input function: F/G inputs

TIF5CK /

TCKIF5

0.55 / 0

1.3 / 0

1.4 / 0

1.5 / 0

ns, min

6-input function: F5IN input

TF5INCK /

TCKF5IN

0.27 / 0

0.6 / 0

0.8 / 0

ns, min

6-input function: F/G inputs via F6 MUX

TIF6CK /

TCKIF6

0.58 / 0

1.3 / 0

1.5 / 0

1.6 / 0

ns, min

BX/BY inputs

TDICK /

TCKDI

0.25 / 0

0.6 / 0

0.7 / 0

0.8 / 0

ns, min

CE input

TCECK /

TCKCE

0.28 / 0

0.55 / 0

0.7 / 0

ns, min

SR/BY inputs (synchronous)

TRCK /

TCKR

0.24 / 0

0.46 / 0

0.52 / 0

0.6 / 0

ns, min

Clock CLK

Minimum Pulse Width, High

TCH

0.56

1.2

1.3

1.4

ns, min

Minimum Pulse Width, Low

TCL

0.56

1.2

1.3

1.4

ns, min

Set/Reset

Minimum Pulse Width, SR/BY inputs

TRPW

0.94

1.9

2.1

2.4

ns, min

Delay from SR/BY inputs to XQ/YQ outputs

(asynchronous)

TRQ

0.39

0.8

0.9

1.0

ns, max

Toggle Frequency (MHz) (for export control)

FTOG

-

416

400

357

MHz

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed “best-case”, but

if a “0” is listed, there is no positive hold time.

相关PDF资料 |

PDF描述 |

|---|---|

| XDMR06A-1 | 7 SEG NUMERIC DISPLAY, RED, 8 mm |

| XH-H | FEMALE, TWO PART BOARD CONNECTOR |

| XHFR-08V-S | 8 CONTACT(S), FEMALE, TWO PART BOARD CONNECTOR |

| XK-1-FREQ-CL | QUARTZ CRYSTAL RESONATOR, 3.2 MHz - 36 MHz |

| XK-1T-FREQ-CL | QUARTZ CRYSTAL RESONATOR, 3.2 MHz - 36 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCV405E-6FG900C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-6FG900I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404I | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG556C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。