参数资料

| 型号: | XR16C2550IMTR-F |

| 厂商: | Exar Corporation |

| 文件页数: | 3/37页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 16B DUAL 48TQFP |

| 标准包装: | 1,500 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 16 字节 |

| 规程: | RS232,RS485 |

| 电源电压: | 2.97 V ~ 5.5 V |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

XR16C2550

11

REV. 1.0.2

2.97V TO 5.5V DUART WITH 16-BYTE FIFO

The 2550 divides the basic external clock by 16. The basic 16X clock provides table rates to support standard

and custom applications using the same system design. The Baud Rate Generator divides the input 16X clock

by any divisor from 1 to 216 -1. The rate table is configured via the DLL and DLM internal register functions.

Customized Baud Rates can be achieved by selecting the proper divisor values for the MSB and LSB sections

of baud rate generator.

Table 5 shows the standard data rates available with a 14.7456 MHz crystal or external clock at 16X sampling

rate. When using a non-standard frequency crystal or external clock, the divisor value can be calculated for

DLL/DLM with the following equation.

2.9

Transmitter

The transmitter section comprises of an 8-bit Transmit Shift Register (TSR) and 16 bytes of FIFO which

includes a byte-wide Transmit Holding Register (THR). TSR shifts out every data bit with the 16X internal

clock. A bit time is 16 clock periods. The transmitter sends the start-bit followed by the number of data bits,

inserts the proper parity-bit if enabled, and adds the stop-bit(s). The status of the FIFO and TSR are reported in

the Line Status Register (LSR bit-5 and bit-6).

2.9.1

Transmit Holding Register (THR) - Write Only

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-0) becomes first data bit to go out. The THR is the input

register to the transmit FIFO of 16 bytes when FIFO operation is enabled by FCR bit-0. Every time a write

operation is made to the THR, the FIFO data pointer is automatically bumped to the next sequential data

location.

2.9.2

Transmitter Operation in non-FIFO Mode

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

divisor (decimal) = (XTAL1 clock frequency) / (serial data rate x 16)

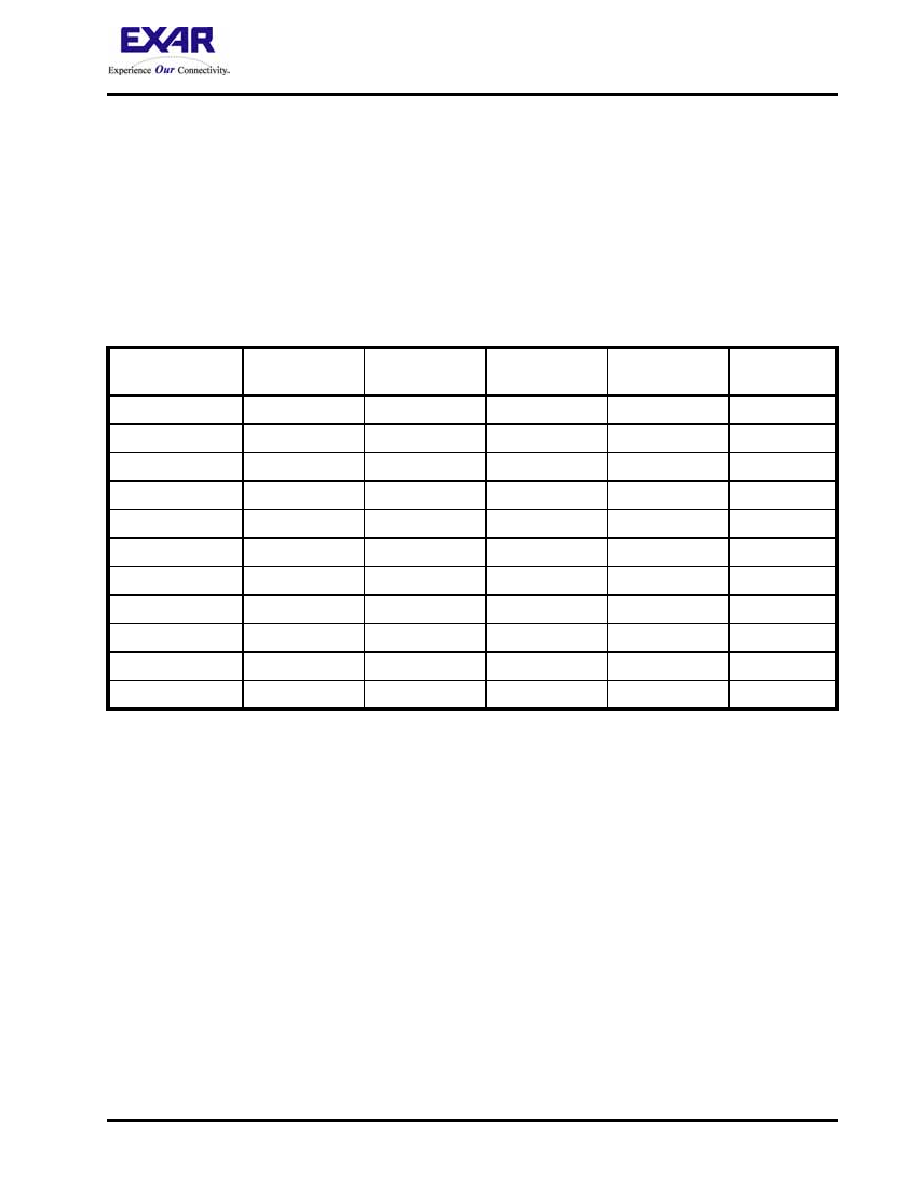

TABLE 5: TYPICAL DATA RATES WITH A 14.7456 MHZ CRYSTAL OR EXTERNAL CLOCK

OUTPUT Data Rate

MCR Bit-7=0

DIVISOR FOR 16x

Clock (Decimal)

DIVISOR FOR 16x

Clock (HEX)

DLM PROGRAM

VALUE (HEX)

DLL PROGRAM

VALUE (HEX)

DATA RATE

ERROR (%)

400

2304

900

09

00

0

2400

384

180

01

80

0

4800

192

C0

00

C0

0

9600

96

60

00

60

0

19.2k

48

30

00

30

0

38.4k

24

18

00

18

0

76.8k

12

0C

00

0C

0

153.6k

6

06

00

06

0

230.4k

4

04

00

04

0

460.8k

2

02

00

02

0

921.6k

1

01

00

01

0

相关PDF资料 |

PDF描述 |

|---|---|

| ST78C34CP40-F | IC UART FIFO 83B 40PDIP |

| XR16M2551IL32TR-F | IC UART FIFO 16B DUAL 32QFN |

| XR16L2551ILTR-F | IC UART FIFO 16B DUAL 32QFN |

| XR16L2750IMTR-F | IC UART FIFO 64B DUAL 48TQFP |

| XR16L2552IJTR-F | IC UART FIFO 16B DUAL 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16C2550IP | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUART WITH 16-BYTE FIFO |

| XR16C2552 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 16-BYTE FIFO |

| XR16C2552IJ | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 16-BYTE FIFO |

| XR16C2850 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS |

| XR16C2850_05 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS |

发布紧急采购,3分钟左右您将得到回复。