- 您现在的位置:买卖IC网 > PDF目录11830 > XR17D158CV-F (Exar Corporation)IC UART PCI BUS OCTAL 144LQFP PDF资料下载

参数资料

| 型号: | XR17D158CV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 38/73页 |

| 文件大小: | 0K |

| 描述: | IC UART PCI BUS OCTAL 144LQFP |

| 产品培训模块: | UART Product Overview |

| 标准包装: | 60 |

| 特点: | * |

| 通道数: | 8 |

| FIFO's: | 64 字节 |

| 规程: | RS485 |

| 电源电压: | 3.3V,5V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

| 其它名称: | 1016-1291 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

xr

XR17D158

REV. 1.2.2

UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART

43

]

ISR[0]: Interrupt Status

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending (default condition).

ISR[3:1]: Interrupt Status

These bits indicate the source for a pending interrupt at interrupt priority levels 1, 2, 3 and 4 (See Interrupt

Source Table 14).

ISR[4]: Xoff/Xon or Special Character Interrupt Status

This bit is enabled when EFR bit-4 is set to a logic 1. ISR bit-4 indicates that the receiver detected a data match

of the Xoff character(s). If this is an Xoff/Xon interrupt, it can be cleared by a read to the ISR. Reading the

XCHAR register will indicate which character (Xoff or Xon) was received last. If it is a special character

interrupt, it can be cleared by reading ISR or it will automatically clear after the next character is received.

ISR[5]: RTS#/CTS# Interrupt Status

This bit is enabled when EFR bit-4 is set to a logic 1. ISR bit-5 indicates that the CTS# or RTS# has changed

state from LOW to HIGH.

ISR[7:6]: FIFO Enable Status

These bits are set to a logic 0 when the FIFOs are disabled. They are set to a logic 1 when the FIFOs are

enabled.

5.8.6

FIFO Control Register (FCR) - Write-Only

This register is used to enable the FIFOs, clear the FIFOs, set the transmit/receive FIFO trigger levels, and

select the DMA mode (legacy term that refers to "block transfer mode"). The DMA and FIFO modes are

defined as follows:

FCR[0]: TX and RX FIFO Enable

Logic 0 = Disable the transmit and receive FIFO (default).

Logic 1 = Enable the transmit and receive FIFOs. This bit must be set to logic 1 when other FCR bits are

written or they will not be programmed.

FCR[1]: RX FIFO Reset

This bit is only active when FCR bit-0 is active.

Logic 0 = No receive FIFO reset (default).

Logic 1 = Reset the receive FIFO pointers and FIFO level counter logic (the receive shift register is not

cleared or altered). This bit will return to a logic 0 after resetting the FIFO.

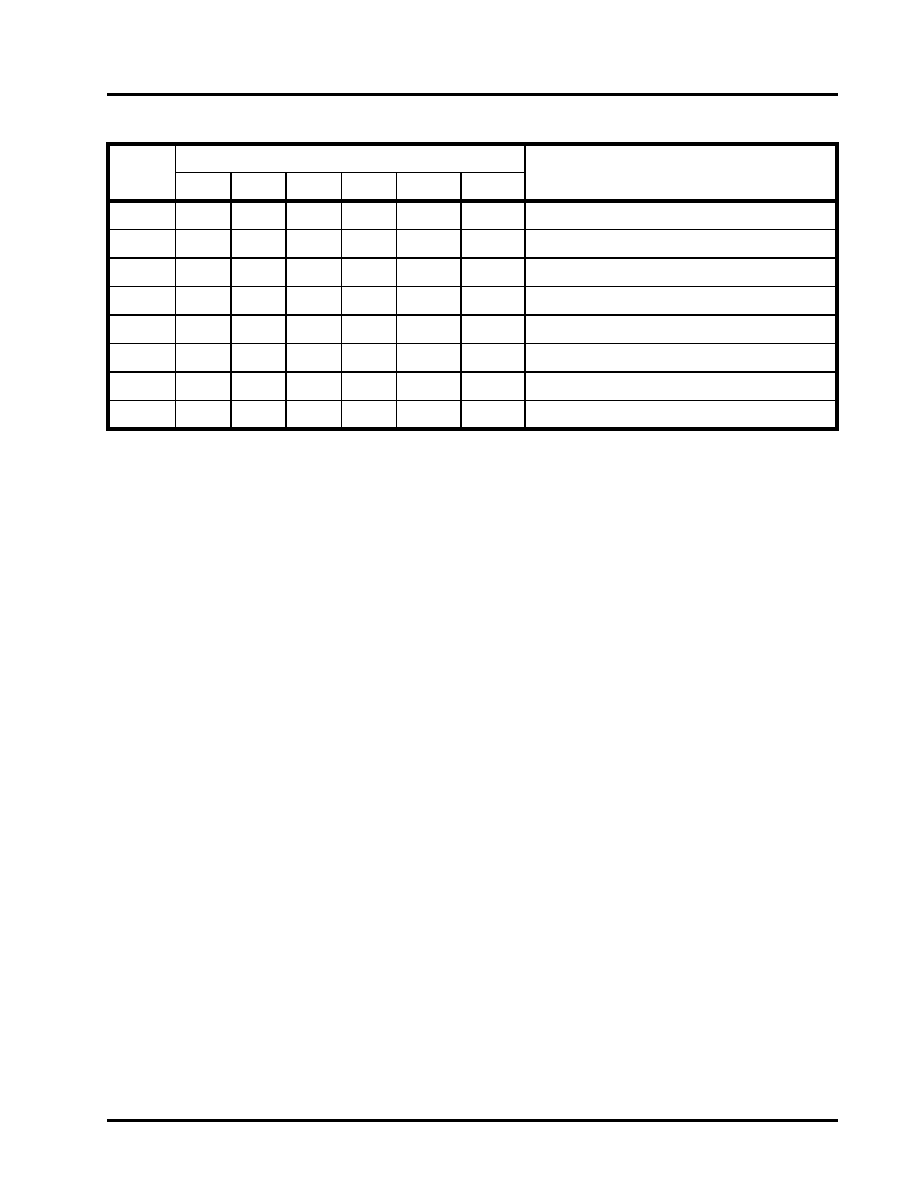

TABLE 14: INTERRUPT SOURCE AND PRIORITY LEVEL

PRIORITY

ISR REGISTER STATUS BITS

SOURCE OF THE INTERRUPT

LEVEL

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

1

0

1

0

LSR (Receiver Line Status Register)

2

0

1

0

RXRDY (Received Data Ready)

3

0

1

0

RXRDY (Receive Data Time-out)

4

0

1

0

TXRDY (Transmitter Holding Register Empty)

5

0

MSR (Modem Status Register)

6

0

1

0

RXRDY (Received Xon/Xoff or Special character)

7

1

0

CTS#/DSR#, RTS#/DTR# change of state

X

0

1

None (default)

相关PDF资料 |

PDF描述 |

|---|---|

| ATMEGA168-15MZ | MCU AVR 16K FLASH 15MHZ 32-QFN |

| XR17V258IVTR-F | IC UART PCI BUS OCTAL 144LQFP |

| XR16L788IQTR-F | IC UART FIFO 64B OCTAL 100QFP |

| XR17C154IV-F | IC UART PCI BUS QUAD 144LQFP |

| XR17C154CV-F | IC UART PCI BUS QUAD 144LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR17D158CV-F-SIWI | 制造商:Exar Corporation 功能描述:FOR WILLIAMS GAMING THEIR CM'S 制造商:EXAR 功能描述:XR17D158CV-F-SIWI 制造商:EXAR 功能描述:FOR WILLIAMS GAMING THEIR CM'S |

| XR17D158CVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D158CVTR-F |

| XR17D158IV | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR17D158IV-F | 功能描述:UART 接口集成电路 3.3V-5V 64B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR17D158IVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D158IVTR-F |

发布紧急采购,3分钟左右您将得到回复。