- 您现在的位置:买卖IC网 > PDF目录11834 > XR88C92CV-F (Exar Corporation)IC UART FIFO DUAL 44LQFP PDF资料下载

参数资料

| 型号: | XR88C92CV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 13/32页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO DUAL 44LQFP |

| 标准包装: | 160 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 16 字节 |

| 电源电压: | 2.97 V ~ 5.5 V |

| 带自动流量控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LQFP |

| 供应商设备封装: | 44-LQFP(10x10) |

| 包装: | 托盘 |

| 其它名称: | XR88C92CV-F-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

XR88C92/192

20

Rev. 1.33

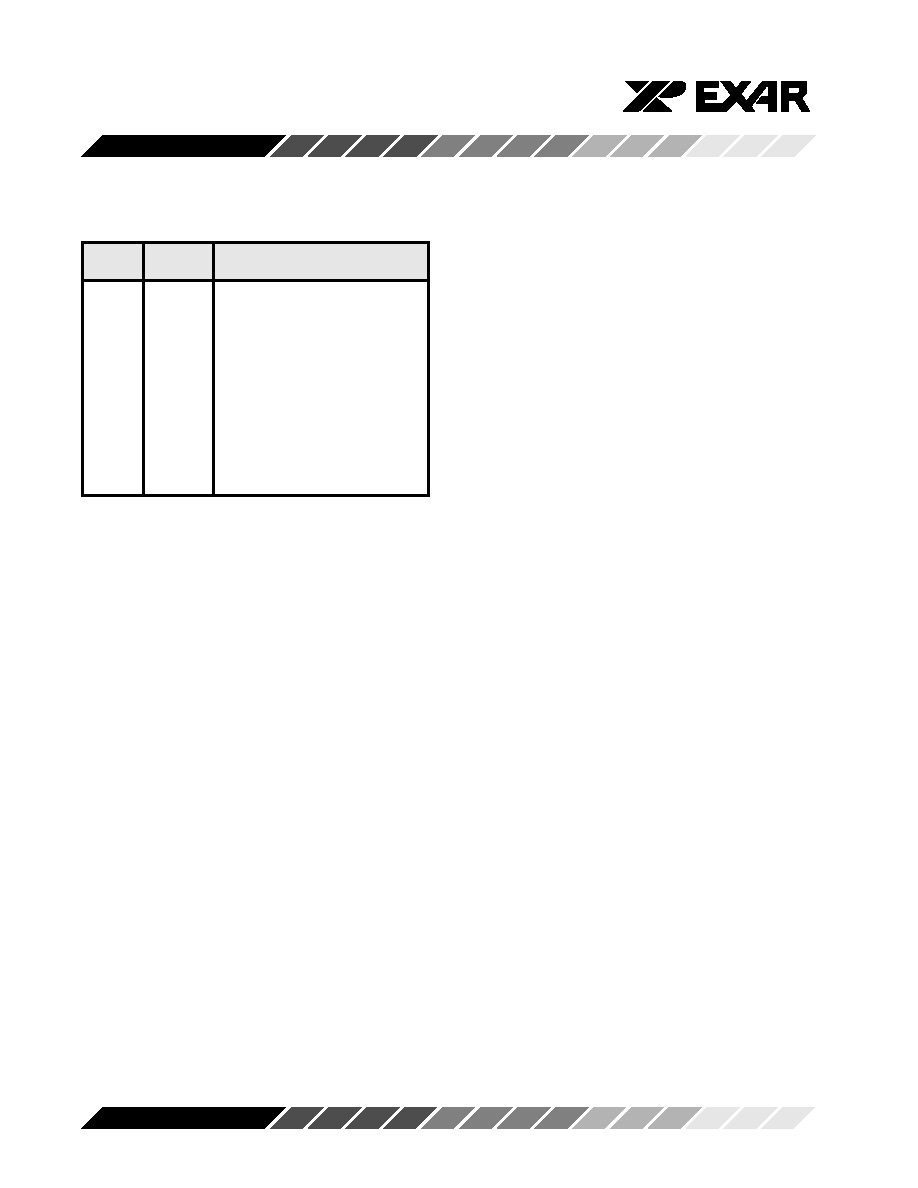

following table shows how to select the clock source for

the C/T when used in counter mode or timer mode.

condition (see MR0A bit-6 and MR1A bit-6). For ex-

ample, if a RX trigger level of '6' is chosen, this bit will

be set whenever the RX FIFO contains six or more

bytes. This bit can be cleared by reading the data out

of the FIFO till it falls below the trigger level.

ISR Bit-2: Channel A change in break.

This bit is set when channel A receiver detects the

beginning or the end of a break condition. It is reset

when the CPU issues a channel A reset break change

interrupt command (CRA bits 7-4 = 0x5).

ISR Bit-3: Counter/Timer (C/T) ready.

In counter mode, this bit is set when the C/T reaches

terminal count. In timer mode, this bit is set each time

the C/T output switches from low to high (rising edge -

see Figure 2). In either mode, this bit is cleared by a stop

counter command.

ISR Bit-4: Transmit ready B.

This bit is set when channel B's transmit buffer (FIFO)

is filled below the programmed transmit trigger level (see

MR0B bits 5-4). For example, if a TX trigger level of '4'

is chosen, this bit will be set whenever the TX FIFO has

four or more empty locations. This bit can be cleared by

loading the TX FIFO above the trigger level.

ISR Bit-5: Receive ready B.

This bit is set when channel B's receive buffer (FIFO)

is filled above the programmed receive trigger level

condition (see MR0B bit-6 and MR1B bit-6). For ex-

ample, if a RX trigger level of '6' is chosen, this bit will

be set whenever the RX FIFO contains six or more

bytes. This bit can be cleared by reading the data out

of the FIFO till it falls below the trigger level.

ISR Bit-6. Channel B change in break.

This bit is set when channel B receiver detects the

beginning or the end of a break condition. It is reset

when the CPU issues a channel B reset break change

interrupt command (CRB bits 7-4 = 0x5).

ISR Bit-7. Input port change status.

This bit is set when a change of state has occurred at

the IP0, IP1, IP2, or IP3 inputs, and that event has been

enabled to cause an interrupt by programming ACR Bits

3-0. This bit is cleared when the CPU reads the input port

change register.

INTERRUPT MASK REGISTER (IMR)

This register selects which bits in the interrupt status

register can cause an interrupt output. If a bit in the

interrupt status register is a “1” and the corresponding

ACR

C/T

Clock Source

Bits 6:4

Mode

0 0 0

Counter

External (IP2)

0 0 1

Counter

TXAClk1-Transmit A 1X clock

0 1 0

Counter

TXBClk1-Transmit B 1X clock

0 1 1

Counter

Crystal or External Clock

(XTAL1/Clk) Divided by 16

1 0 0

Timer

External (IP2)

1 0 1

Timer

External (IP2) Divided by 16

1 1 0

Timer

Crystal or External Clock

(XTAL1/Clk)

1 1 1

Timer

Crystal or External Clock

(XTAL1/Clk) Divided by 16

ACR Bit-7: Baud rate table Select.

This bit is used to select between two sets of baud rate

tables. See Baudrate table on Page 18. It should be

changed only after both channels have been reset and

disabled.

0 = Set 1

1 = Set 2

INTERRUPT STATUS REGISTER (ISR)

This register provides the status of all potential interrupt

sources. The contents of this register are logically

“AND”-ed with the contents of the interrupt mask regis-

ter, and the results are “OR”-ed. The resulting signal is

inverted to produce the -INT output. All active interrupt

sources are visible by reading the ISR, regardless of

the contents of the interrupt mask register. Reading

the ISR has no effect on any interrupt source. Each

active interrupt source must be cleared in a source-

specific fashion to clear the ISR. All interrupt sources

are cleared when the XR88C92/192 is reset.4

ISR Bit-0: Transmit ready A.

This bit is set when channel A's transmit buffer (FIFO)

is filled below the programmed transmit trigger level (see

MR0A bits 5-4). For example, if a TX trigger level of '4'

is chosen, this bit will be set whenever the TX FIFO has

four or more empty locations. This bit can be cleared by

loading the TX FIFO above the trigger level.

ISR Bit-1: Receive ready A .

This bit is set when channel A's receive buffer (FIFO)

is filled above the programmed receive trigger level

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/20WC98S | CONN RCPT 10POS WALL MNT W/SCKT |

| XR88C681J-F | IC UART CMOS DUAL 44PLCC |

| ST16C552AIJ68-F | IC UART FIFO 16B DUAL 68PLCC |

| MS27474T10A98P | CONN RCPT 6POS JAM NUT W/PINS |

| XR88C192IV-F | IC UART FIFO DUAL 44LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR88C92CVTR-F | 功能描述:UART 接口集成电路 Dual Channel UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR88C92IJ | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL UNIVERSAL ASYNCHRONOUS RECEIVER AND TRANSMITTER |

| XR88C92IJ-F | 功能描述:UART 接口集成电路 Dual Channel UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR88C92IJTR-F | 功能描述:UART 接口集成电路 Dual Channel UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR88C92IP | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL UNIVERSAL ASYNCHRONOUS RECEIVER AND TRANSMITTER |

发布紧急采购,3分钟左右您将得到回复。