- 您现在的位置:买卖IC网 > PDF目录16988 > XRD98L62EVAL (Exar Corporation)EVAL BOARD XRD98L62 PDF资料下载

参数资料

| 型号: | XRD98L62EVAL |

| 厂商: | Exar Corporation |

| 文件页数: | 3/37页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD XRD98L62 |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

11

Rev. P2.00

XRD98L62

Preliminary

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Offset

OB[7]

OB[6]

OB[5]

OB[4]

OB[3]

OB[2]

OB[1]

OB[0]

Default

0010000000

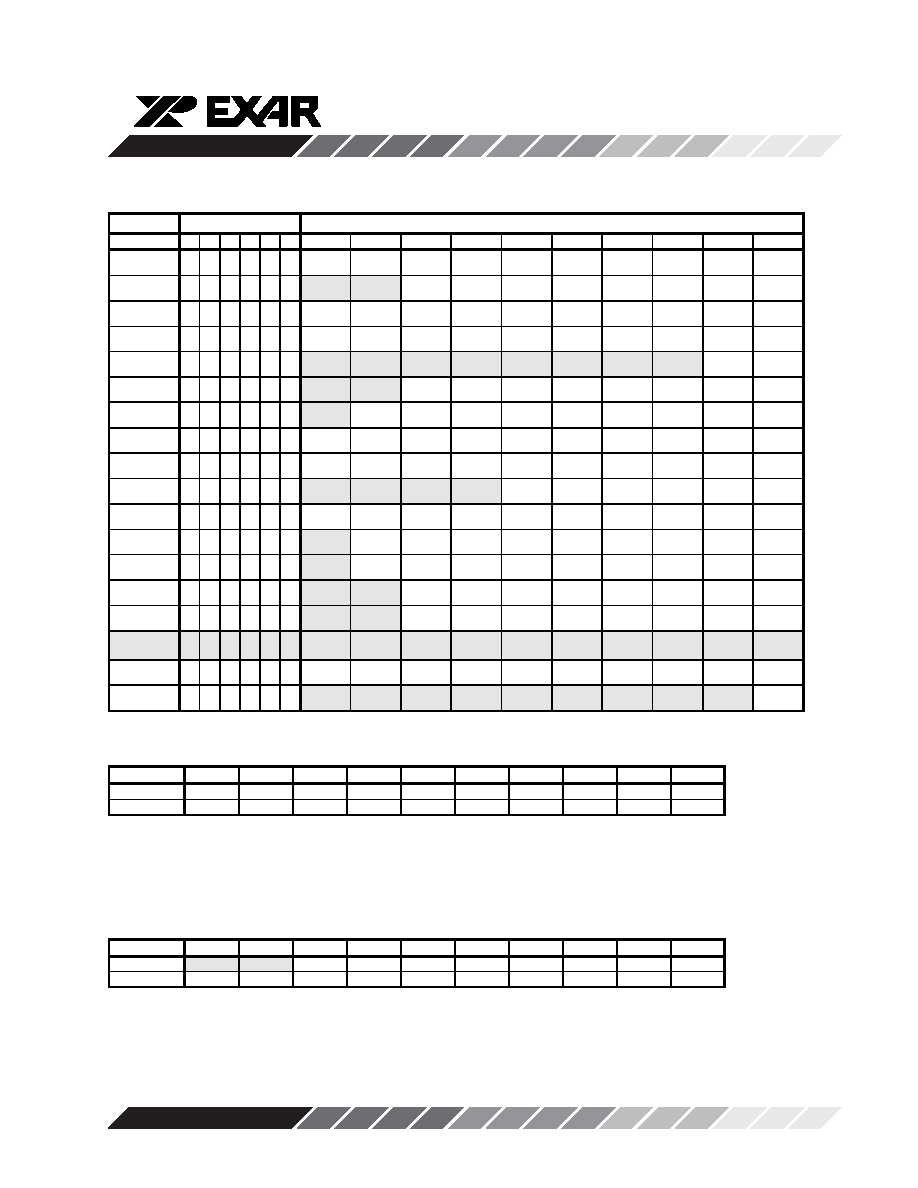

Offset Register (Reg. 1, Address 000001)

The Offset register is used to set the target ADC output code for Optical Black pixels.

See the Black Level Offset Calibration section for more information.

Table 1. Serial Interface Register Address Map & default values

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Gain

PGA[9]

PGA[8]

PGA[7]

PGA[6]

PGA[5]

PGA[4]

PGA[3]

PGA[2]

PGA[1]

PGA[0]

Default

0000000000

The Gain register is used to set the gain of the Programmable Gain Amplifier (PGA).

Code 0000000000 is minimum gain (0 dB). Codes 1011111111 and greater are maximum gain (36 dB).

See the Programmable Gain Amplifier (PGA) section for more information.

Gain Register (Reg. 0, Address 000000)

Address bits

Data bits

Reg. Name A5 A4 A3 A2 A1 A0

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Gain

0

00000

PGA[9]

0

PGA[8]

0

PGA[7]

0

PGA[6]

0

PGA[5]

0

PGA[4]

0

PGA[3]

0

PGA[2]

0

PGA[1]

0

PGA[0]

0

Offset

0

00001

OB[7]

1

OB[6]

0

OB[5]

0

OB[4]

0

OB[3]

0

OB[2]

0

OB[1]

0

OB[0]

0

Calibration

0

00010

Avg[2]

1

Avg[1]

0

Avg[0]

1

Mode

0

LFrame

0

DNS[1]

1

DNS[0]

1

FastCal

1

Hold

0

ManCal

0

Wait A

0

00011

WL[11]

0

WL[10]

0

WL[9]

0

WL[8]

0

WL[7]

0

WL[6]

0

WL[5]

0

WL[4]

0

WL[3]

0

WL[2]

0

Wait B

0

00100

WL[1]

0

WL[0]

1

OB Lines

0

00101

OBL[7]

0

OBL[6]

0

OBL[5]

0

OBL[4]

0

OBL[3]

0

OBL[2]

0

OBL[1]

1

OBL[0]

0

CDAC

0

00110

CDAC[8]

0

CDAC[7]

0

CDAC[6]

0

CDAC[5]

0

CDAC[4]

0

CDAC[3]

0

CDAC[2]

0

CDAC[1]

0

CDAC[0]

0

FDAC

0

00111

FDAC[9]

0

FDAC[8]

0

FDAC[7]

0

FDAC[6]

0

FDAC[5]

0

FDAC[4]

0

FDAC[3]

0

FDAC[2]

0

FDAC[1]

0

FDAC[0]

0

Control

0

01000

DIGtest

0

ADCtest

0

NoCDS

0

LowPwr

0

OE

1

DAC1pd

1

DAC0pd

1

AFEpd

0

ADCpd

0

PwrDwn

0

Polarity

0

01001

SBLKpol

0

SPIXpol

0

CALpol

0

CLAMPpol

0

FRpol

0

ADCpol

0

Clock

0

01010

CLKtest

0

nullamp

0

cmset

0

fastclk

0

CLAMPopt

0

OneShot

0

ClampCal

0

SPIXopt

0

RSTreject

0

VSreject

0

Delay A

0

01011

DelayA[8]

0

DelayA[7]

0

DelayA[6]

0

DelayA[5]

0

DelayA[4]

0

DelayA[3]

0

DelayA[2]

0

DelayA[1]

0

DelayA[0]

0

Delay B

0

01100

DelayB[8]

0

DelayB[7]

0

DelayB[6]

0

DelayB[5]

0

DelayB[4]

0

DelayB[3]

0

DelayB[2]

0

DelayB[1]

0

DelayB[0]

0

DAC0

0

01101

DAC0[7]

0

DAC0[6]

0

DAC0[5]

0

DAC0[4]

0

DAC0[3]

0

DAC0[2]

0

DAC0[1]

0

DAC0[0]

0

DAC1

0

01110

DAC1[7]

0

DAC1[6]

0

DAC1[5]

0

DAC1[4]

0

DAC1[3]

0

DAC1[2]

0

DAC1[1]

0

DAC1[0]

0

ReadBack

1

11110

RBenable

0

RBreg[8]

0

RBreg[7]

0

RBreg[6]

0

RBreg[5]

0

RBreg[4]

0

RBreg[3]

0

RBreg[2]

0

RBreg[1]

0

RBreg[0]

0

Reset

1

11111

Reset

0

相关PDF资料 |

PDF描述 |

|---|---|

| XRD98L61ZEVAL | EVAL BOARD FOR XRD98L61AIV |

| LGU2G391MELB | CAP ALUM 390UF 400V 20% SNAP |

| ECC31DCMT | CONN EDGECARD 62POS .100 WW |

| 1589448-3 | STRIP CON |

| AD8335-EVALZ | BOARD EVALUATION FOR AD8335 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRD98L62ZEVAL | 功能描述:数据转换 IC 开发工具 Eval Board (Solder) XRD98L62AIV RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| XRD98L63 | 制造商:EXAR 制造商全称:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L63AIV | 制造商:EXAR 制造商全称:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L63AIV-F | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| XRD98L63AIVTR-F | 制造商:Exar Corporation 功能描述:AFE General Purpose 1ADC 12-Bit 3V 48-Pin TQFP T/R 制造商:Exar Corporation 功能描述:XRD98L63AIVTR-F |

发布紧急采购,3分钟左右您将得到回复。