参数资料

| 型号: | XRT73L03BIV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 46/61页 |

| 文件大小: | 0K |

| 描述: | IC LIU E3/DS3/STS-1 3CH 120LQFP |

| 标准包装: | 72 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 3/3 |

| 规程: | DS3,E3,STS-1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-LQFP(14x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

XRT73L03B

3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

REV. 1.0.1

48

b. Operating in the Hardware Mode

To configure Channel (n) to operate in the Analog Lo-

cal Loop-Back Mode, set the LLB_(n) input pin “High"

and the RLB_(n) input pin "Low".

4.2

THE DIGITAL LOCAL LOOP-BACK MODE.

When a given channel is configured to operate in the

Digital Local Loop-Back Mode, the channel ignores

any signals that are input to the RTIP and RRing in-

put pins. The Transmitting Terminal Equipment trans-

mits clock and data into the XRT73L03B via the TP-

Data, TNData and TxClk input pins. This data is pro-

cessed through the Transmit Clock Duty Cycle Adjust

PLL and the HDB3/B3ZS Encoder block. At this

point, this data is looped back to the HDB3/B3ZS De-

coder block. After this post-Loop-Back data has been

processed through the HDB3/B3ZS Decoder block, it

outputs to the Near-End Receiving Terminal Equip-

ment via the RPOS, RNEG and RxClk output pins.

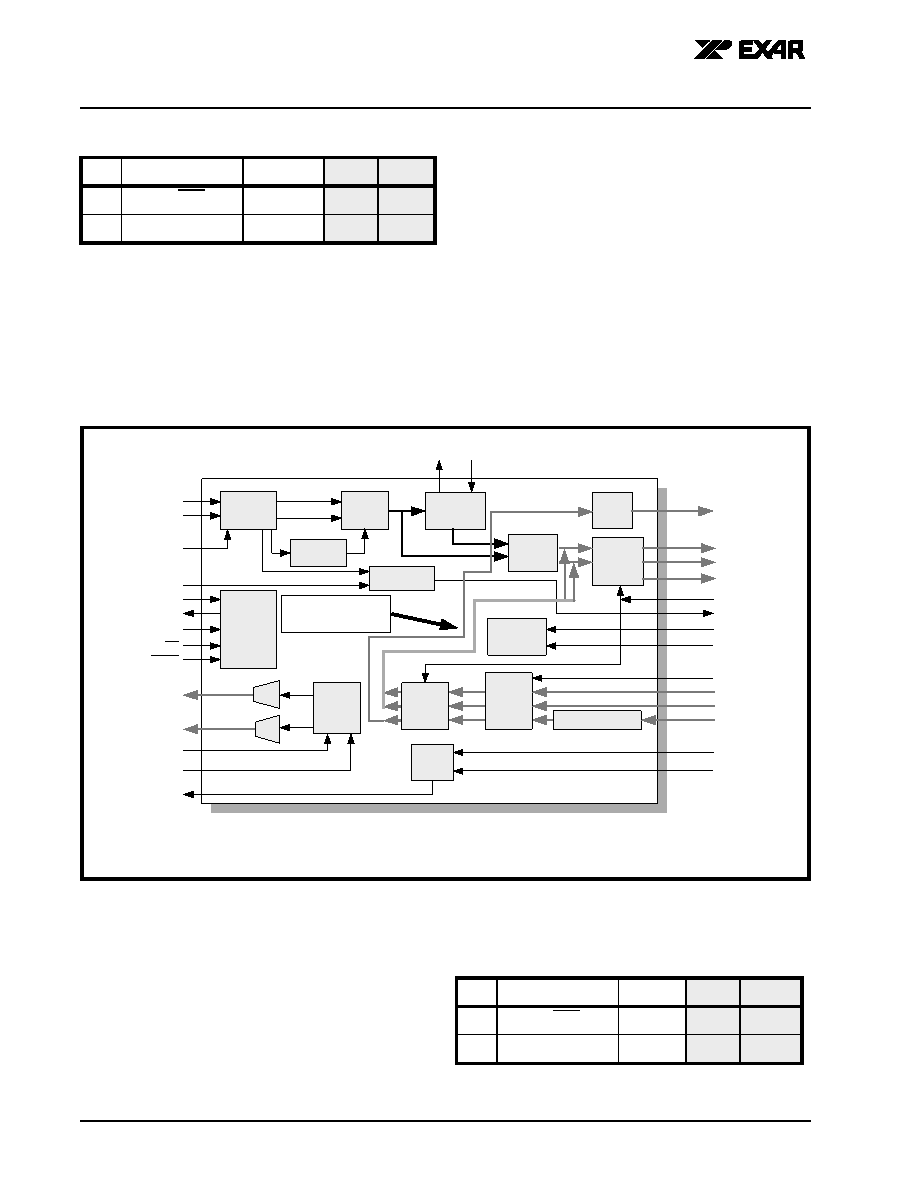

Figure 34 illustrates the path that the data takes when

the chip is configured to operate in the Digital Local

Loop-Back Mode.

Configure a channel to operate in the Digital Local

Loop-Back Mode by employing either one of the fol-

lowing two-steps:

a. Operating in the Host Mode

To configure Channel (n) to operate in the Digital Lo-

cal Loop-Back Mode, write a "1" into both the LLB

and RLB bit-fields within Command Register CR4-(n).

b. Operating in the Hardware Mode.

COMMAND REGISTER CR4-(n)

D4

D3

D2

D1

D0

X

STS-1/DS3_(n)

E3_(n)

LLB_(n) RLB_(n)

XX

X

1

0

FIGURE 34. THE DIGITAL LOCAL LOOP-BACK PATH WITHIN A GIVEN CHANNEL

AGC/

Equalizer

Peak

Detector

LOS Detector

Slicer

Clock

Recovery

Data

Recovery

Invert

Loop MUX

HDB3/

B3ZS

Decoder

LOSTHR_(n)

SDI

SDO

SClk

CS

REGR

RTIP_(n)

RRing_(n)

REQEN_(n)

RxClk_(n)

RPOS_(n)

RNEG_(n)

LCV(_n)

ENDECDIS

RLOS_(n)

LLB_(n)

RLB_(n)

TAOS_(n)

TPData(_n)

TNData_(n)

TxClk_(n)

Notes: 1. (n) = 0, 1 or 2 for respective Channels

2. Serial Processor Interface input pins are shared by the three Channels in HOST Mode and redefined in

Hardware Mode.

RLOL_(n) EXClk_(n)

Device

Monitor

MTIP_(n)

MRing(_n)

Transmit

Logic

Duty Cycle Adjust

TxLEV_(n)

TxOFF_(n)

DMO_(n)

TTIP_(n)

TRing_(n)

Pulse

Shaping

HDB3/

B3ZS

Encoder

Serial

Processor

Interface

Digital Local

Loop-Back Path

COMMAND REGISTER CR4-(n)

D4

D3

D2

D1

D0

X

STS-1/DS3_(n)

E3_(n)

LLB_(n) RLB_(n)

XX

X

1

相关PDF资料 |

PDF描述 |

|---|---|

| XRT73L04BIV-F | IC LIU E3/DS3/STS-1 4CH 144LQFP |

| XRT73L06IB-F | IC LIU E3/DS3/STS-1 6CH 217BGA |

| XRT73LC00AIV-F | IC LIU STS1/DS3/E3 SGL 44TQFP |

| XRT73LC03AIV-F | IC LIU E3/DS3/STS-1 3CH 120LQFP |

| XRT73LC04AIV-F | IC LIU E3/DS3/STS-1 4CH 144LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT73L03IV | 制造商:EXAR 制造商全称:EXAR 功能描述:3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT |

| XRT73L03IVS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XRT73L04A | 制造商:EXAR 制造商全称:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04AIV | 制造商:EXAR 制造商全称:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L04B | 制造商:EXAR 制造商全称:EXAR 功能描述:4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

发布紧急采购,3分钟左右您将得到回复。