参数资料

| 型号: | XRT75R06DIB-F |

| 厂商: | Exar Corporation |

| 文件页数: | 59/105页 |

| 文件大小: | 0K |

| 描述: | IC LIU E3/DS3/STS-1 6CH 217BGA |

| 标准包装: | 126 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 6/6 |

| 规程: | DS3,E3,STS-1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 217-BBGA |

| 供应商设备封装: | 217-BGA(23x23) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页

á

XRT75R06D

SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

REV. 1.0.0

52

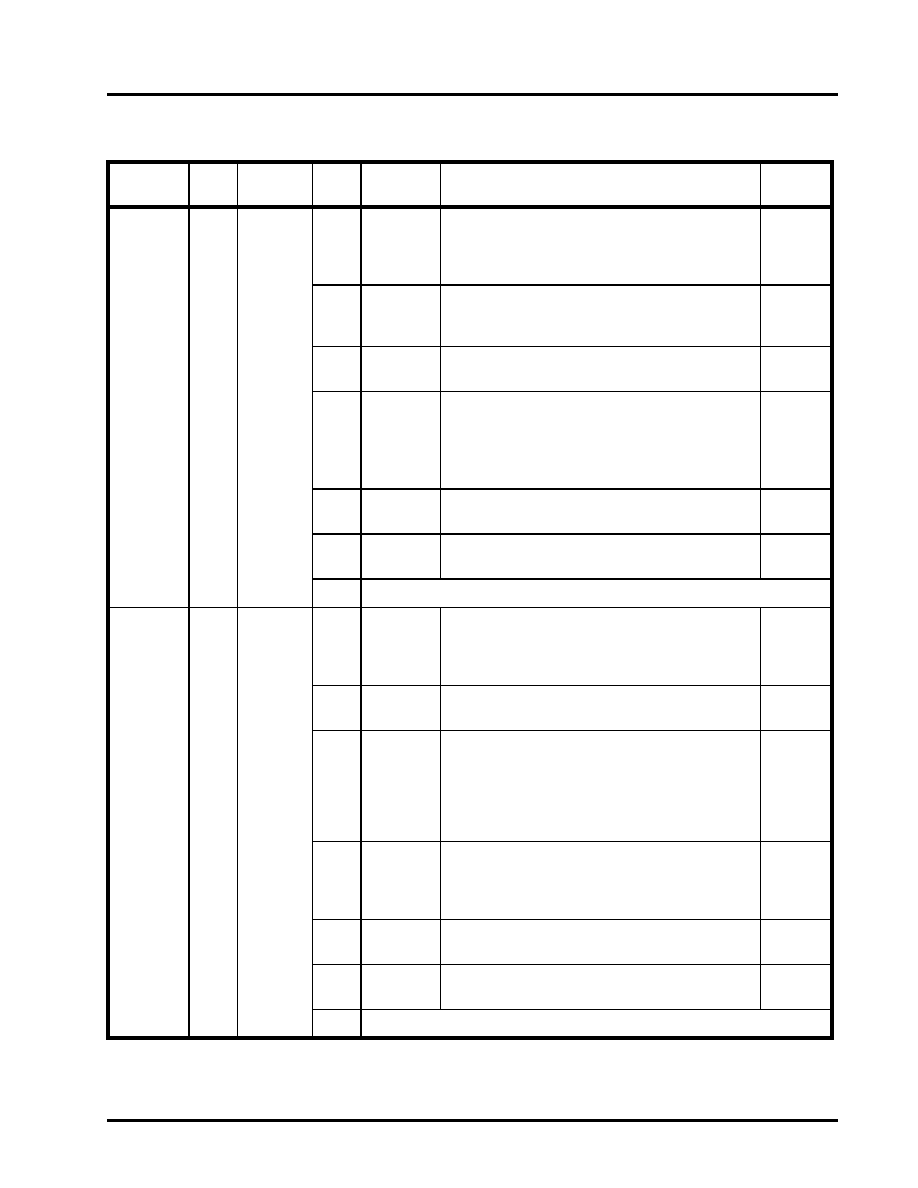

TABLE 18: REGISTER MAP DESCRIPTION - CHANNEL N

ADDRESS

(HEX)

TYPE

REGISTER

NAME

BIT#

SYMBOL

DESCRIPTION

DEFAULT

VALUE

0x01 (ch 0)

0x11 (ch 1)

0x21 (ch 2)

0x31 (ch 3)

0x41 (ch 4)

0x51 (ch 5)

R/W

Interrupt

Enable

(source

level)

D0

DMOIE_n

If the Driver Monitor (connected to the output of the

channel) detects the absence of pulses for 128 con-

secutive cycles, it will set the interrupt flag if this bit

has been set.

0

D1

RLOSIE_n This flag will allow a loss of receive signal(for that

channel) to send an interrupt to the Host when this

bit is set.

0

D2

RLOLIE_n

This flag will allow a loss of lock condition to send an

interrupt to the Host when this bit is set.

0

D3

FLIE_n

Set this bit to enable the interrupt when the FIFO

Limit of the Jitter Attenuator is within 2 bits of over-

flow/underflow condition.

NOTE: This bit field is ignored when the Jitter Atten-

uator is disabled.

0

D4

PRBSERIE

_n

Set this bit to enable the interrupt when the PRBS

error is detected.

0

D5

PRBSERC

NTIE_n

Set this bit to enable the interrupt when the PRBS

error count register saturates.

0

D6-D7

Reserved

0x02 (ch 0)

0x12 (ch 1)

0x22 (ch 2)

0x32 (ch 3)

0x42 (ch 4)

0x52 (ch 5)

Reset

on

Read

Interrupt

Status

(source

level)

D0

DMOIS_n

If the Drive monitor circuot detects the absence of

pulses for 128 consecutive cycles, t will set this

interrupt status flag (if enabled) This bit is set on a

change of state of the DMO circuit.

0

D1

RLOSIS_n This flag will indicate a change of “loss of Receive

signal” to the Host when this bit is set.

0

D2

RLOLIS_n

This flag will allow a change in the loss of lock condi-

tion to send an interrupt to the Host when this bit is

enabled.Loss of lock is defined as a difference of

greater than 0.5% between the recovered clock and

the channel’s reference clock. Any change (return to

lock) will trigger the interrupt status flag again.

0

D3

FLIS_n

This bit will generate an interrupt if the jitter attenua-

tor FIFO reaches (or leaves) a limit condition. This

limit condition is defined as the FIFO being within

two counts of full or empty.

0

D4

PRBSERIS

_n

This bit is set when the PRBS error occurs.

0

D5

PRBSERC

NTIS_n

This bit is set when the PRBS error count register

saturates.

0

D7-D6

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| XRT75R06IB-F | IC LIU E3/DS3/STS-1 6CH 217BGA |

| XRT75R12DIB-L | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| XRT75R12IB-L | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| XRT75VL00DIV | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| XRT75VL00IV-F | IC LIU E3/DS3/STS-1 1CH 52TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT75R06ES | 功能描述:时钟合成器/抖动清除器 6CH T3/E3/STS1LIU+JA 3.3V W/REDUNDANCY RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| XRT75R06IB | 功能描述:外围驱动器与原件 - PCI 6CH E3/DS3/STS1 LIU+Jitter Attenuato RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT75R06IB208 | 制造商:Exar Corporation 功能描述:Line Interface Unit 51.84Mbps DS3/E3/STS-1 Parallel 217-Pin BGA |

| XRT75R06IB-F | 功能描述:外围驱动器与原件 - PCI 6 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XRT75R12 | 制造商:EXAR 制造商全称:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

发布紧急采购,3分钟左右您将得到回复。