参数资料

| 型号: | XRT75R12IB-L |

| 厂商: | Exar Corporation |

| 文件页数: | 15/90页 |

| 文件大小: | 0K |

| 描述: | IC LIU E3/DS3/STS-1 12CH 420TBGA |

| 标准包装: | 40 |

| 类型: | 线路接口装置(LIU) |

| 驱动器/接收器数: | 12/12 |

| 规程: | DS3,E3,STS-1 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 420-LBGA 裸露焊盘 |

| 供应商设备封装: | 420-TBGA(35x35) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页

XRT75R12

19

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

REV. 1.0.4

2.0

CLOCK SYNTHESIZER

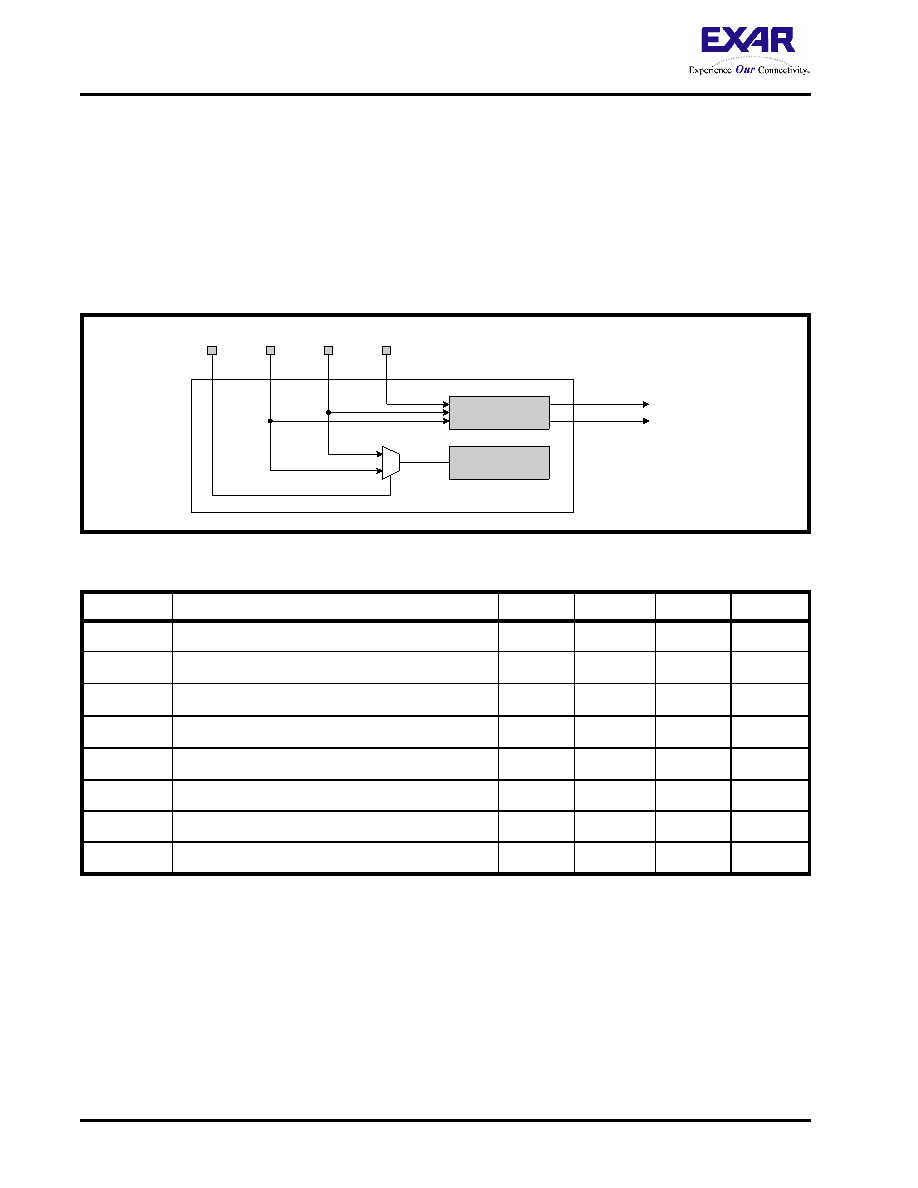

The LIU uses a flexible user interface for accepting clock references to generate the internal master clocks

used to drive the LIU. The reference clock used to supply the microprocessor timing is generated from the DS-

3 or SFM clock input. Therefore, if the chip is configured for STS-1 only or E3 only, then the DS-3 input pin

must be connected to the STS-1 pin or E3 pin respectively. In DS-3 mode or when SFM is used, the STS-1

and E3 input pins can be left unconnected. If SFM is enabled by pulling the SFM_EN pin "High", 12.288MHz is

the only clock reference necessary to generate DS-3, E3, or STS-1 line rates and the microprocessor timing.

A simplified block diagram of the clock synthesizer is shown in Figure 3. Reference clock performance

specifications can be found on Table 2 below.

NOTES:

1.

Required to meet Bellcore GR-499 specification on frequency stability requirements.

However, the LIU can

functionally operate with ±100 ppm without meeting the required specifications.

2.

Reference clock jitter limits are required for the transmit output to meet ITU-T and Bellcore system level jitter

requirements.

FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE INPUT CLOCK CIRCUITRY DRIVING THE MICROPROCESSOR

TABLE 2: REFERENCE CLOCK PERFORMANCE SPECIFICATIONS

SYMBOL

PARAMETER

MIN

TYP

MAX

UNITS

REFDUTY

Reference Clock Duty Cycle

40

60

%

REFE3

E3 Reference Clock Frequency Tolerance1

-20

+20

ppm

REFDS3

DS3 Reference Clock Frequency Tolerance1

-20

+20

ppm

REFSTS1

STS-1 Reference Clock Frequency Tolerance1

-20

+20

ppm

REFSFM

SFM Reference Clock Frequency Tolerance1

-20

+20

ppm

tRISE_REFCLK Reference Clock Rise Time (10% to 90%)

5

ns

tFALL_REFCLK Reference Clock Fall Time (90% to 10%)

5

ns

CLKJIT

Reference Clock Jitter Stability2

0.005

UIp2p

Clock Synthesizer

Processor

LOL_n

DS3Clk

SFM_EN

STS-1Clk/12M

E3Clk

CLKOUT_n

0

1

相关PDF资料 |

PDF描述 |

|---|---|

| XRT75VL00DIV | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| XRT75VL00IV-F | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| XRT79L71IB-F | IC LIU/FRAMER DS3/E3 1CH 208BGA |

| XRT81L27IV-F | IC LIU EI 7CH 3.3V 128TQFP |

| XRT82D20IW-F | IC LIU E1 SGL 28SOJ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT75VL00 | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00_08 | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00D | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75VL00D_08 | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

| XRT75VL00D1V-F | 制造商:Exar Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。