- 您现在的位置:买卖IC网 > PDF目录4227 > 24FC1026T-I/SM (Microchip Technology)IC EEPROM 1024KB 1MHZ 8-SOIJ PDF资料下载

参数资料

| 型号: | 24FC1026T-I/SM |

| 厂商: | Microchip Technology |

| 文件页数: | 7/28页 |

| 文件大小: | 0K |

| 描述: | IC EEPROM 1024KB 1MHZ 8-SOIJ |

| 标准包装: | 2,100 |

| 格式 - 存储器: | EEPROMs - 串行 |

| 存储器类型: | EEPROM |

| 存储容量: | 1M (128K x 8) |

| 速度: | 400kHz,1MHz |

| 接口: | I²C,2 线串口 |

| 电源电压: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 8-SOIC(0.209",5.30mm 宽) |

| 供应商设备封装: | 8-SOIJ |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

�� �

�

�

�24AA1026/24LC1026/24FC1026�

�4.0� BUS� CHARACTERISTICS�

�The� following� bus� protocol� has� been� defined:�

�?� Data� transfer� may� be� initiated� only� when� the� bus�

�is� not� busy.�

�?� During� data� transfer,� the� data� line� must� remain�

�stable� whenever� the� clock� line� is� high.� Changes� in�

�the� data� line� while� the� clock� line� is� high� will� be�

�The� data� on� the� line� must� be� changed� during� the� low�

�period� of� the� clock� signal.� There� is� one� bit� of� data� per�

�clock� pulse.�

�Each� data� transfer� is� initiated� with� a� Start� condition� and�

�terminated� with� a� Stop� condition.� The� number� of� the�

�data� bytes� transferred� between� the� Start� and� Stop�

�conditions� is� determined� by� the� master� device.�

�interpreted� as� a� Start� or� Stop� condition.�

�4.5�

�Acknowledge�

�Accordingly,� the� following� bus� conditions� have� been�

�defined� (� Figure� 4-1� ).�

�Each� receiving� device,� when� addressed,� is� obliged� to�

�generate� an� Acknowledge� signal� after� the� reception� of�

�4.1�

�Bus� Not� Busy� (A)�

�each� byte.� The� master� device� must� generate� an� extra�

�clock� pulse� which� is� associated� with� this� Acknowledge�

�Both� data� and� clock� lines� remain� high.�

�bit.�

�4.2� Start� Data� Transfer� (B)�

�A� high-to-low� transition� of� the� SDA� line� while� the� clock�

�(SCL)� is� high� determines� a� Start� condition.� All�

�commands� must� be� preceded� by� a� Start� condition.�

�Note:�

�The� 24XX1026� does� not� generate� any�

�Acknowledge� bits� if� an� internal� program-�

�ming� cycle� is� in� progress,� however,� the�

�control� byte� that� is� being� polled� must�

�match� the� control� byte� used� to� initiate� the�

�write� cycle.�

�4.3�

�Stop� Data� Transfer� (C)�

�A� device� that� acknowledges� must� pull-down� the� SDA�

�line� during� the� Acknowledge� clock� pulse� in� such� a� way�

�A� low-to-high� transition� of� the� SDA� line� while� the� clock�

�(SCL)� is� high� determines� a� Stop� condition.� All�

�operations� must� end� with� a� Stop� condition.�

�that� the� SDA� line� is� stable� low� during� the� high� period� of�

�the� acknowledge� related� clock� pulse.� Of� course,� setup�

�and� hold� times� must� be� taken� into� account.� During�

�reads,� a� master� must� signal� an� end� of� data� to� the� slave�

�4.4�

�Data� Valid� (D)�

�by� NOT� generating� an� Acknowledge� bit� on� the� last� byte�

�that� has� been� clocked� out� of� the� slave.� In� this� case,� the�

�The� state� of� the� data� line� represents� valid� data� when,�

�after� a� Start� condition,� the� data� line� is� stable� for� the�

�duration� of� the� high� period� of� the� clock� signal.�

�slave� (24XX1026)� will� leave� the� data� line� high� to� enable�

�the� master� to� generate� the� Stop� condition.�

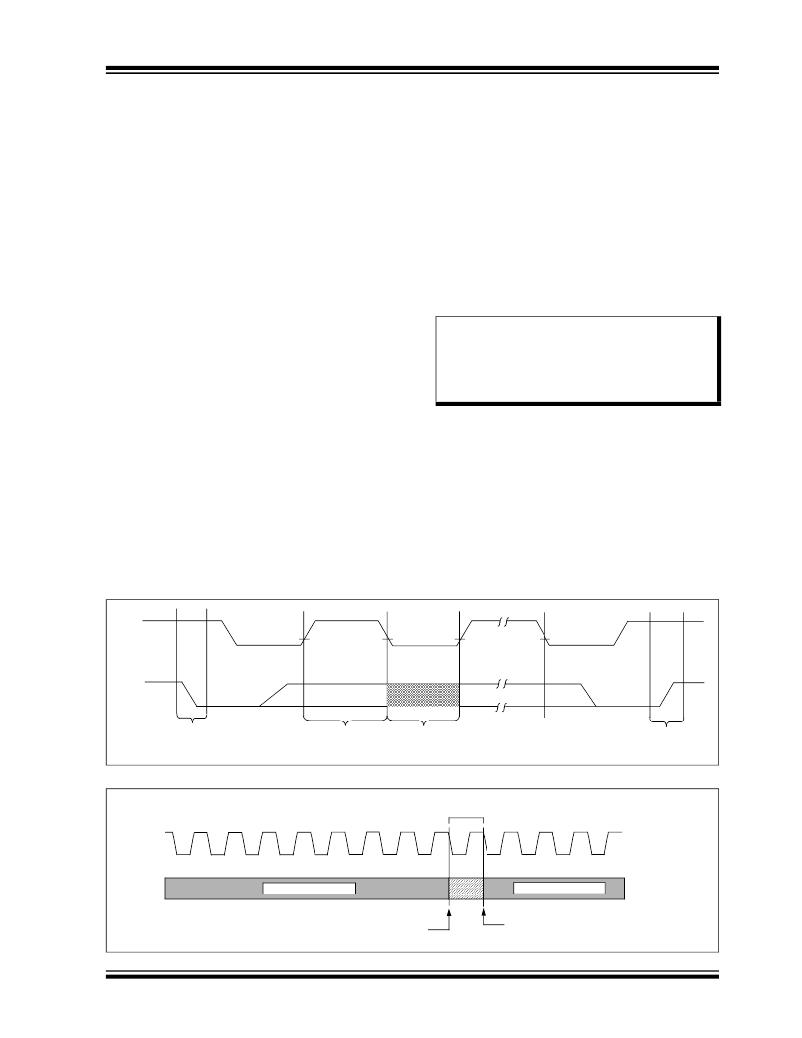

�FIGURE� 4-1:�

�DATA� TRANSFER� SEQUENCE� ON� THE� SERIAL� BUS�

�(A)�

�(B)�

�(D)�

�(D)�

�(C)�

�(A)�

�SCL�

�SDA�

�Start�

�Condition�

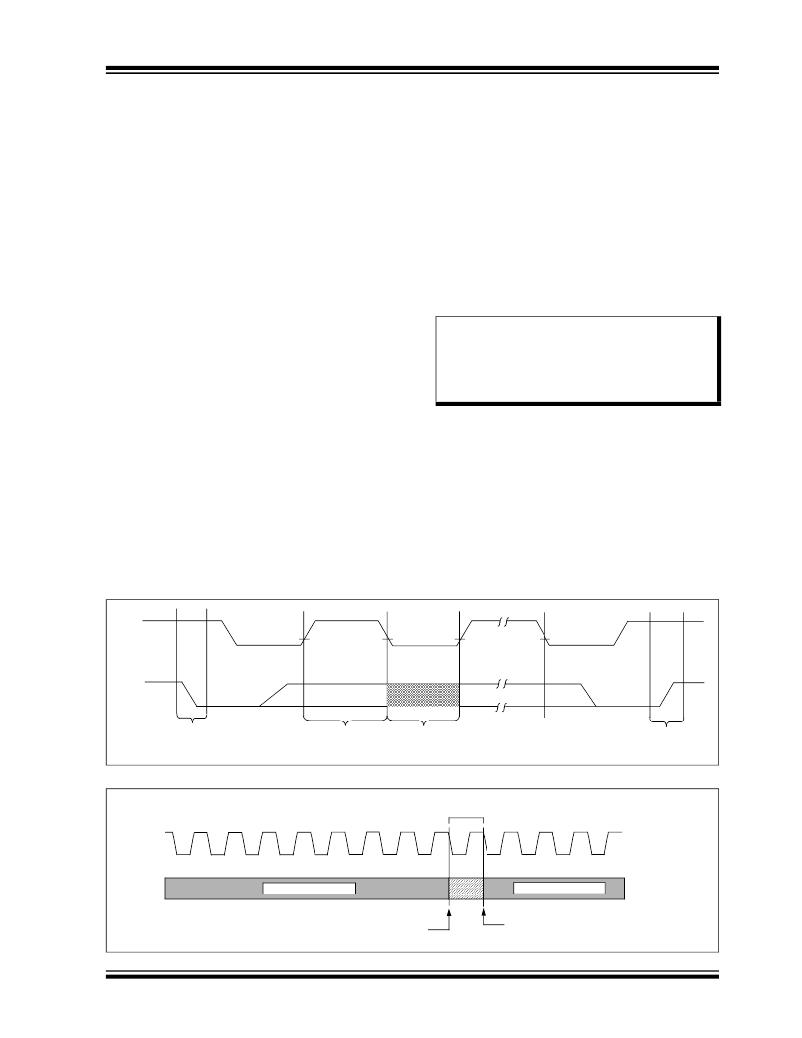

�FIGURE� 4-2:�

�Address� or�

�Acknowledge�

�Valid�

�ACKNOWLEDGE� TIMING�

�Data�

�Allowed�

�To� Change�

�Stop�

�Condition�

�Acknowledge�

�Bit�

�SCL�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�1�

�2�

�3�

�SDA�

�Data from transmitter�

�Data from transmitter�

�The� transmitter� must� release� the� SDA� line� at� this�

�point� allowing� the� receiver� to� pull� the� SDA� line� low�

�to� acknowledge� the� previous� eight� bits� of� data.�

�?� 2011-2012� Microchip� Technology� Inc.�

�The� receiver� must� release� the� SDA� line� at� this�

�point� so� the� transmitter� can� continue� sending�

�data.�

�DS22270C-page� 7�

�相关PDF资料 |

PDF描述 |

|---|---|

| AMC10DTEN | CONN EDGECARD 20POS .100 EYELET |

| SST25VF064C-80-4C-Q2AE-T | IC FLASH SER 64M DUAL I/O 8WSON |

| AMC10DTEH | CONN EDGECARD 20POS .100 EYELET |

| SST25VF064C-80-4C-Q2AE | IC FLASH SER 64M DUAL I/O 8WSON |

| ASC60DRTS | CONN EDGECARD 120PS .100 DIP SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 24FC128 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:128K I2C CMOS Serial EEPROM |

| 24FC128-E/CS15K | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:128K I2Ca?¢ CMOS Serial EEPROM |

| 24FC128-E/MC | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:128K I2C CMOS Serial EEPROM |

| 24FC128E/MF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EEPROM |

| 24FC128-E/MF | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:128K I2C CMOS Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。