- 您现在的位置:买卖IC网 > PDF目录33351 > 2SB768 2000 mA, 150 V, PNP, Si, SMALL SIGNAL TRANSISTOR, TO-252 PDF资料下载

参数资料

| 型号: | 2SB768 |

| 元件分类: | 小信号晶体管 |

| 英文描述: | 2000 mA, 150 V, PNP, Si, SMALL SIGNAL TRANSISTOR, TO-252 |

| 封装: | MP-3Z, 3 PIN |

| 文件页数: | 1/4页 |

| 文件大小: | 531K |

| 代理商: | 2SB768 |

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics

sales representative for availability and additional information.

SILICON POWER TRANSISTOR

2SB768

PNP SILICON TRIPLE DIFFUSED TRANSISTOR

DATA SHEET

Document No. D18264EJ4V0DS00 (4th edition)

(Previous No. TC-1625A)

Date Published July 2006 NS CP(K)

Printed in Japan

1985, 2006

The mark <R> shows major revised points.

The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

DESCRIPTION

The 2SB768 is designed for Color TV Vertical Deflection Output,

especially in Hybrid Integrated Circuits.

FEATURES

High Voltage: VCEO =

150 V

Complement to 2SD1033

ABSOLUTE MAXIMUM RATINGS (TA = 25

°C)

Collector to Base Voltage

VCBO

200

V

Collector to Emitter Voltage

VCEO

150

V

Emitter to Base Voltage

VEBO

5

V

Collector Current (DC)

IC(DC)

2

A

Collector Current (pulse)

Note 1

IC(pulse)

3

A

Total Power Dissipation (TA = 25

°C) Note 2

PT

2.0

W

Junction Temperature

Tj

150

°C

Storage Temperature

Tstg

55 to +150

°C

Notes 1. PW

≤ 10 ms, Duty Cycle ≤ 50%

2. When mounted on ceramic substrate of 7.5 cm

2 × 0.7 mm

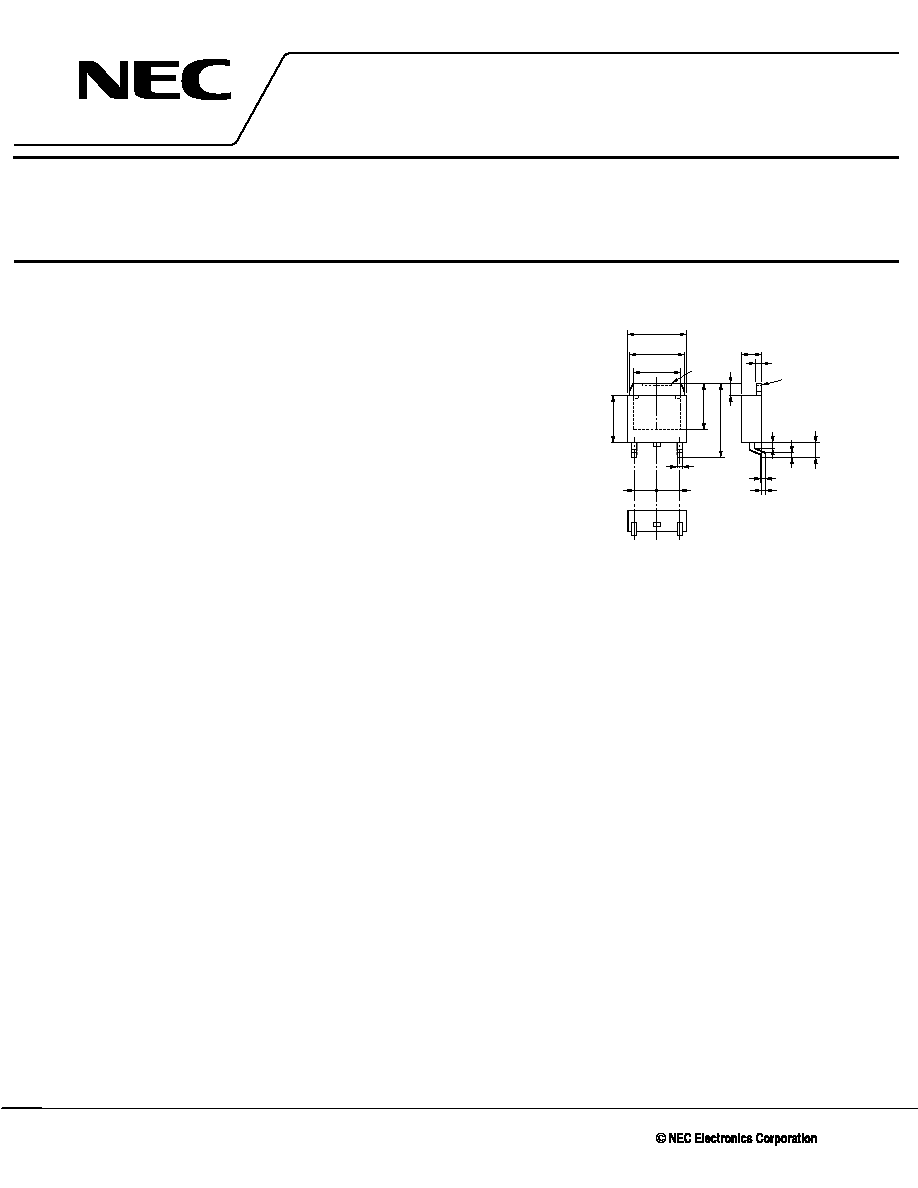

PACKAGE DRAWING (Unit: mm)

12 3

4

6.5 ±0.2

4.4 ±0.2

5.0 ±0.2

0.5 ±0.1

5.6

±0.3

9.5

±0.5

2.5

±0.5

1.0

±0.5

1.5

0.1

+0.2

2.3 ±0.2

0.5 ±0.1

Note

0.4

MIN.

0.5

TYP.

0.15 ±0.15

2.3 ±0.3

5.5

±0.2

TO-252 (MP-3Z)

1. Base

2. Collector

3. Emitter

4. Collector Fin

Note The depth of notch at the top of the fin is

from 0 to 0.2 mm.

<R>

相关PDF资料 |

PDF描述 |

|---|---|

| 2SB768M | 2000 mA, 150 V, PNP, Si, SMALL SIGNAL TRANSISTOR, TO-252 |

| 2SB768K | 2000 mA, 150 V, PNP, Si, SMALL SIGNAL TRANSISTOR, TO-252 |

| 2SB772-O-BP | 3 A, 30 V, PNP, Si, POWER TRANSISTOR, TO-126 |

| 2SB772-GR-BP | 3 A, 30 V, PNP, Si, POWER TRANSISTOR, TO-126 |

| 2SB772-Y-BP | 3 A, 30 V, PNP, Si, POWER TRANSISTOR, TO-126 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 2SB768-AZ(L) | 制造商:Renesas Electronics 功能描述:PNP Bulk |

| 2SB768-E1-AZ | 制造商:Renesas Electronics Corporation 功能描述:Trans GP BJT PNP 150V 2A 3-Pin(2+Tab) TO-252 T/R Cut Tape |

| 2SB768K | 制造商:NEC 制造商全称:NEC 功能描述:BJT |

| 2SB768-K-AZ | 制造商:Renesas Electronics Corporation 功能描述: |

| 2SB768L | 制造商:NEC 制造商全称:NEC 功能描述:BJT |

发布紧急采购,3分钟左右您将得到回复。