- 您现在的位置:买卖IC网 > PDF目录21904 > 4421-DKDB2 (Silicon Laboratories Inc)KIT DEV TEST EZRADIO SI4421 TRX PDF资料下载

参数资料

| 型号: | 4421-DKDB2 |

| 厂商: | Silicon Laboratories Inc |

| 文件页数: | 13/45页 |

| 文件大小: | 0K |

| 描述: | KIT DEV TEST EZRADIO SI4421 TRX |

| 标准包装: | 1 |

| 附件类型: | 测试卡,收发器,434MHz |

| 适用于相关产品: | EZRadio? |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

�� �

�

Si4421�

�CONTROL� INTERFACE�

�Commands� to� the� transmitter� are� sent� serially.� Data� bits� on� pin� SDI� are� shifted� into� the� device� upon� the� rising� edge� of� the� clock� on�

�pin� SCK� whenever� the� chip� select� pin� nSEL� is� low.� When� the� nSEL� signal� is� high,� it� initializes� the� serial� interface.� All� commands�

�consist� of� a� command� code,� followed� by� a� varying� number� of� parameter� or� data� bits.� All� data� are� sent� MSB� first� (e.g.� bit� 15� for� a� 16-�

�bit� command).� Bits� having� no� influence� (don’t� care)� are� indicated� with� X.� Special� care� must� be� taken� when� the� microcontroller’s� built-�

�in� hardware� serial� port� is� used.� If� the� port� cannot� be� switched� to� 16-bit� mode� then� a� separate� I/O� line� should� be� used� to� control� the�

�nSEL� pin� to� ensure� the� low� level� during� the� whole� duration� of� the� command� or� a� software� serial� control� interface� should� be�

�implemented.� The� Power-On� Reset� (POR)� circuit� sets� default� values� in� all� control� and� command� registers.�

�The� receiver� will� generate� an� interrupt� request� (IT)� for� the� microcontroller� -� by� pulling� the� nIRQ� pin� low� -� on� the� following� events:�

�?� The� TX� register� is� ready� to� receive� the� next� byte� (RGIT)�

�?� The� RX� FIFO� has� received� the� preprogrammed� amount� of� bits� (FFIT)�

�?� Power-on� reset� (POR)�

�?� RX� FIFO� overflow� (FFOV)� /� TX� register� underrun� (RGUR)�

�?� Wake-up� timer� timeout� (WKUP)�

�?� Negative� pulse� on� the� interrupt� input� pin� nINT� (EXT)�

�?� Supply� voltage� below� the� preprogrammed� value� is� detected� (LBD)�

�FFIT� and� FFOV� are� applicable� when� the� RX� FIFO� is� enabled.� RGIT� and� RGUR� are� applicable� only� when� the� TX� register� is� enabled.� To�

�identify� the� source� of� the� IT,� the� status� bits� should� be� read� out.�

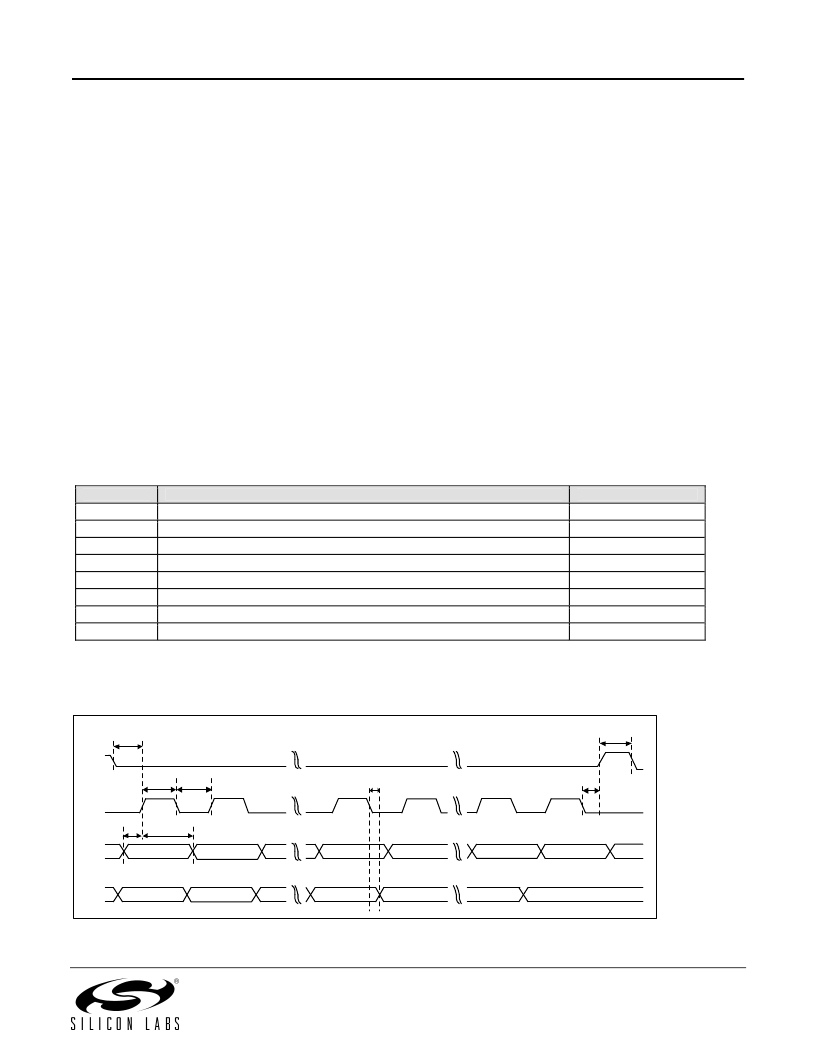

�Timing� Specification�

�Symbol�

�t� CH�

�t� CL�

�t� SS�

�t� SH�

�t� SHI�

�t� DS�

�t� DH�

�t� OD�

�Parameter�

�Clock� high� time�

�Clock� low� time�

�Select� setup� time� (nSEL� falling� edge� to� SCK� rising� edge)�

�Select� hold� time� (SCK� falling� edge� to� nSEL� rising� edge)�

�Select� high� time�

�Data� setup� time� (SDI� transition� to� SCK� rising� edge)�

�Data� hold� time� (SCK� rising� edge� to� SDI� transition)�

�Data� delay� time�

�Minimum� value� [ns]�

�25�

�25�

�10�

�10�

�25�

�5�

�5�

�10�

�Timing� Diagram�

�nSEL�

�t� SS�

�t� SHI�

�t� CH�

�t� CL�

�t� OD�

�t� SH�

�SCK�

�t� DS�

�t� DH�

�SDI�

�SDO�

�BIT� 15�

�FFIT�

�BIT� 14�

�FFOV�

�BIT� 13�

�BIT� 8�

�CRL�

�BIT� 7�

�AT� S�

�BIT� 1�

�OFFS(0)�

�BIT� 0�

�FIFO� OUT�

�13�

�相关PDF资料 |

PDF描述 |

|---|---|

| 4420-DKDB2 | KIT DEV TEST EZRADIO SI4420 TRX |

| 4421-DKDB1 | KIT DEV TEST EZRADIO SI4421 TRX |

| 4322-DKDB1 | KIT DEV TEST EZRADIO SI4322 RX |

| 4021-DKDB13 | KIT DEV TEST EZRADIO SI4021 TX |

| ASPI-0418FS-KIT | INDUCTOR KIT SHIELD ASPI |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 4421-DKDB5 | 功能描述:射频开发工具 Test Board BIFA TRx (868MHz) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| 4421-DQ0025 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Heavy Duty Incremental Rotary Shaft Encoder |

| 4421-DQ4096 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Heavy Duty Incremental Rotary Shaft Encoder |

| 4421-DS0025 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Heavy Duty Incremental Rotary Shaft Encoder |

| 4421-DS4096 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Heavy Duty Incremental Rotary Shaft Encoder |

发布紧急采购,3分钟左右您将得到回复。