- 您现在的位置:买卖IC网 > PDF目录298413 > 5962-9960702QXA 512K X 8 STANDARD SRAM, 25 ns, CDFP36 PDF资料下载

参数资料

| 型号: | 5962-9960702QXA |

| 元件分类: | SRAM |

| 英文描述: | 512K X 8 STANDARD SRAM, 25 ns, CDFP36 |

| 封装: | BOTTOM BRAZED, SHIELDED, DFP-36 |

| 文件页数: | 1/15页 |

| 文件大小: | 121K |

| 代理商: | 5962-9960702QXA |

FEATURES

q 20ns (3.3 volt supply) maximum address access time

q Asynchronous operation for compatibility with industry-

standard 512K x 8 SRAMs

q TTL compatible inputs and output levels, three-state

bidirectional data bus

q Typical radiation performance

- Total dose: 50krads

- >100krads(Si), for any orbit, using Aeroflex UTMC

patented shielded package

- SEL Immune >80 MeV-cm

2 /mg

- LETTH(0.25) = >10 MeV-cm

2/mg

- Saturated Cross Section cm2 per bit, 5.0E-9

- <1E-8 errors/bit-day, Adams 90% geosynchronous

heavy ion

q Packaging options:

- 36-lead ceramic flatpack (3.42 grams)

- 36-lead flatpack shielded (10.77 grams)

q Standard Microcircuit Drawing 5962-99607

- QML T and Q compliant

INTRODUCTION

The QCOTSTM UT8Q512 Quantified Commercial Off-the-

Shelf product is a high-performance CMOS static RAM

organized as 524,288 words by 8 bits. Easy memory

expansion is provided by an active LOW Chip Enable (E),

an active LOW Output Enable (G), and three-state drivers.

This device has a power-down feature that reduces power

consumption by more than 90% when deselected

.

Writing to the devicei s accomplished by taking Chip Enable

one (E) input LOW and Write Enable (W) inputs LOW.

Data on the eight I/O pins (DQ0 through DQ7) is then written

into the location specified on the address pins (A0 through

A

18 ). Reading from the device is accomplished by taking

Chip Enable one (E) and Output Enable (G) LOW while

forcing Write Enable (W) HIGH. Under these conditions,

the contents of the memory location specified by the address

pins will appear on the I/O pins.

The eight input/output pins (DQ

0 through DQ 7) are placed

in a high impedance state when the device is deselected (E,

HIGH), the outputs are disabled (G HIGH), or during a write

operation (E LOWand W LOW).

Standard Products

QCOTS

TM UT8Q512 512K x 8 SRAM

Data Sheet

November 13, 2002

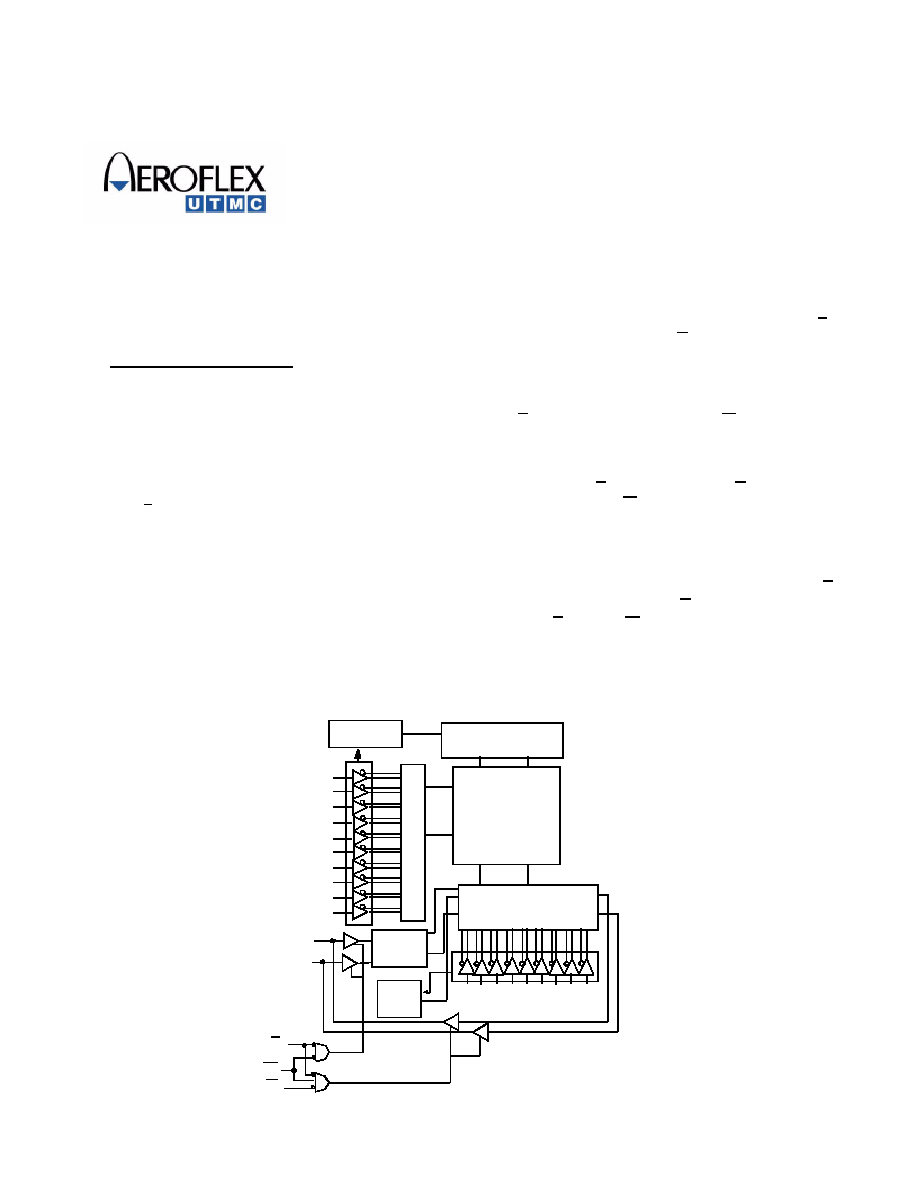

Memory Array

1024 Rows

512x8 Columns

Pre-Charge Circuit

Clk. Gen.

R

o

w

S

e

le

c

t

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O Circuit

Column Select

Data

Control

CLK

Gen.

A

1

0

A

11

A

1

2

A

1

3

A

1

4

A

1

5

A

1

6

A

1

7

A

1

8

DQ

0 - DQ7

W

G

E

Figure 1. UT8Q512 SRAM Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| 5962D0153301QXX | 512K X 32 MULTI DEVICE SRAM MODULE, 35 ns, QMA68 |

| 5962F0151601VYA | 8K X 8 OTPROM, 55 ns, CDFP28 |

| 5962F0323601QXX | 128K X 32 STANDARD SRAM, 15 ns, CQFP68 |

| 5962F9565802VCC | ACT SERIES, TRIPLE 3-INPUT NAND GATE, CDIP14 |

| ACTS10HMSR | ACT SERIES, TRIPLE 3-INPUT NAND GATE, UUC16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9960801HUA | 制造商:International Rectifier 功能描述:Module DC-DC 1-OUT 5V 16A 80W 12-Pin AFL 制造商:International Rectifier 功能描述:DC TO DC CONVERTER 120 TO 5VDC 80W - Rail/Tube |

| 5962-9960901HZC | 制造商:International Rectifier 功能描述:MICROCIRCUIT, HYBRID, |

| 5962-9961001HXA | 功能描述:模数转换器 - ADC Dual 12 Bit105 MSPS MCM RoHS:否 制造商:Analog Devices 通道数量: 结构: 转换速率: 分辨率: 输入类型: 信噪比: 接口类型: 工作电源电压: 最大工作温度: 安装风格: 封装 / 箱体: |

| 5962-9961002HXA | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 12-bit Parallel 68-Pin CLCC 制造商:Analog Devices 功能描述:ADC DUAL PIPELINED 105MSPS 12-BIT PARALLEL 68CLCC - Bulk 制造商:Analog Devices Inc. 功能描述:Analog to Digital Converters - ADC Dual 12 Bit 105 MSPS A/D Converter MCM 制造商:Analog Devices Inc. 功能描述:Analog to Digital Converters - ADC Dual 12 Bit105 MSPS MCM 制造商:Analog Devices 功能描述:CONVERTER - ADC |

| 5962-9961502QYA | 制造商:e2v Aerospace & Defense 功能描述:Trans JFET N-CH 3-Pin TO-206AA 制造商:e2v Aerospace & Defense 功能描述:MEMORY, 64K X 9 CASCADABLE FIFO, 15 NS ACCESS TIME |

发布紧急采购,3分钟左右您将得到回复。