- 您现在的位置:买卖IC网 > PDF目录293971 > 5962D1022901QXC 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 PDF资料下载

参数资料

| 型号: | 5962D1022901QXC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 |

| 封装: | CERAMIC, QFP-128 |

| 文件页数: | 8/68页 |

| 文件大小: | 1475K |

| 代理商: | 5962D1022901QXC |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

16

Operating Mode

The normal operating mode is selected by setting M7 and M8 to zero; the other combinations of values for M7 and M8 are reserved

for future use and/or test modes. The programmed burst length applies to both READ and WRITE bursts. Test modes and reserved

states should not be used because unknown operation or incompatibility with future versions may result.

WRITE Burst Mode

When M9 = 0, BL programmed via M0–M2 applies to both READ and WRITE bursts; when M9 = 1, the programmed burst length

applies to READ burst, but write accesses are single-location (nonburst) accesses.

COMMANDS

Table 5 provides a quick reference of available commands. This is followed by a written description of each command. Three

additional Truth Tables appear in the Operations section; these tables provide current state/next state information.

Notes:

1. CKE is HIGH for all commands shown.

2. A0–A11 define the op-code written to the mode register, and A12 should be driven LOW.

3. A0–A12 provide row address, and BA0, BA1 determine which bank is made active.

4. A0–A9, A11 provide column address; A10 HIGH enables the auto precharge feature (nonpersistent), while A10 LOW disables the auto precharge feature; BA0, BA1

determine which bank is being read from or written to.

5. A10 LOW: BA0, BA1 determine the bank being precharged. A10 HIGH: All banks precharged and BA0, BA1 are “Don’t Care.”

6. This command is AUTO REFRESH if CKE is HIGH.

7. Internal refresh counter controls row addressing; all inputs and I/Os are “Don’t Care” except for CKE.

8. Activates or deactivates the DQs during WRITEs (zero-clock delay) and READs (two-clock delay).

COMMAND INHIBIT

The COMMAND INHIBIT function prevents new commands from being executed by the SDRAM, regardless of whether the CLK

signal is enabled. The SDRAM is effectively deselected. Operations already in progress are not affected.

NO OPERATION (NOP)

The NO OPERATION (NOP) command is used to perform a NOP to an SDRAM that is selected (CS# is LOW). This prevents

unwanted commands from being registered during idle or wait states. Operations already in progress are not affected.

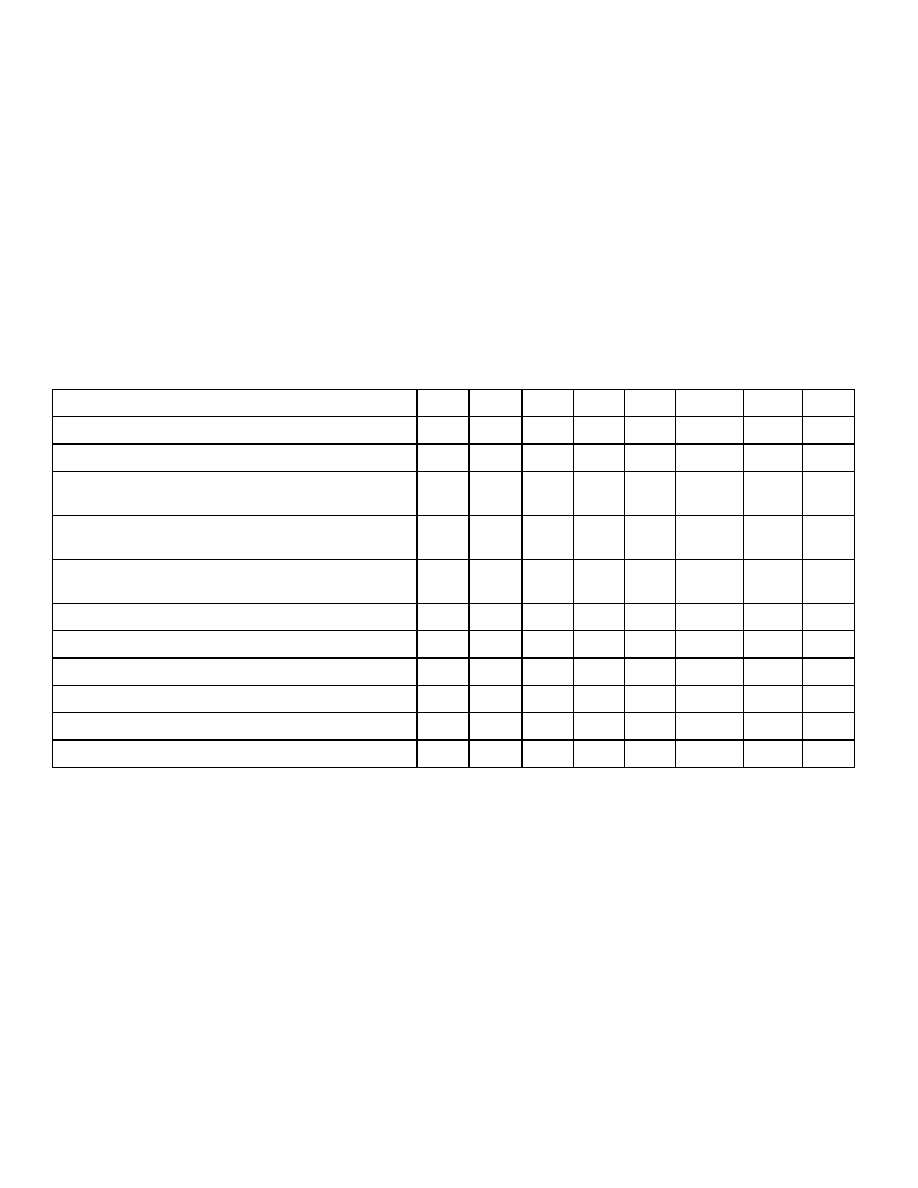

Table 5: Truth Table 1 Commands and DQM Operation

Name (Function)

CS#

RAS# CAS# WE# DQM Address

DQs

Notes

COMMAND INHIBIT (NOP)

H

X

NO OPERATION (NOP)

L

H

X

ACTIVE (Select bank and activate row)

L

H

X

Bank/

row

X

3

READ (Select bank and column, and start READ burst)

L

H

L

H

L/H8

Bank/

col

X

4

WRITE (Select bank and column, and start WRITE burst)

L

H

L

L/H8

Bank/

col

Valid

4

BURST TERMINATE

L

H

L

X

Active

PRECHARGE (Deactivate row in bank or banks)

L

H

L

X

Code

X

5

AUTO REFRESH

L

H

X

6, 7

LOAD MODE REGISTER

L

X

Op-code

X

4

Write enable/output enable

--

L

--

Active

8

Write inhibit/output High-Z

--

H

--

High-Z

8

相关PDF资料 |

PDF描述 |

|---|---|

| 5962F0253401VXC | 2.5 V FIXED POSITIVE REGULATOR, CDFP16 |

| L491333DIE2V | 3.3 V FIXED POSITIVE REGULATOR, UUC |

| 5962F9654403QXA | OTHER DECODER/DRIVER, CDFP16 |

| 5962F9657601QCX | AC SERIES, 4-BIT LOOK-AHEAD CARRY GENERATOR, TRUE OUTPUT, CDIP16 |

| 5962F9657701VXC | ACT SERIES, 4-BIT LOOK-AHEAD CARRY GENERATOR, TRUE OUTPUT, CDFP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962D9563201VXC | 制造商:STMicroelectronics 功能描述:RS-432LINE DRIVERQUADFLAT16, GOLD - Bulk |

| 5962D9666301VXC | 制造商:STMicroelectronics 功能描述:RS-432LINE DRIVERQUADFLAT16, GOLD - Bulk |

| 5962F0052301QXC | 制造商:Intersil Corporation 功能描述: |

| 5962F0052301VXC | 制造商:Intersil Corporation 功能描述: |

| 5962F0151001VXC | 制造商:Intersil Corporation 功能描述:RAD SEU HARD QUAD COMPARATOR, CLASS V - Bulk |

发布紧急采购,3分钟左右您将得到回复。