- 您现在的位置:买卖IC网 > PDF目录19568 > 5M80ZT100I5N (Altera)IC MAX V CPLD 80 LE 100-TQFP PDF资料下载

参数资料

| 型号: | 5M80ZT100I5N |

| 厂商: | Altera |

| 文件页数: | 7/30页 |

| 文件大小: | 0K |

| 描述: | IC MAX V CPLD 80 LE 100-TQFP |

| 产品培训模块: | Max V Overview |

| 特色产品: | MAX? V CPLDs |

| 标准包装: | 90 |

| 系列: | MAX® V |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 7.5ns |

| 电压电源 - 内部: | 1.71 V ~ 1.89 V |

| 逻辑元件/逻辑块数目: | 80 |

| 宏单元数: | 64 |

| 输入/输出数: | 79 |

| 工作温度: | -40°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP |

| 供应商设备封装: | 100-TQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�Chapter� 3:� DC� and� Switching� Characteristics� for� MAX� V� Devices�

�Operating� Conditions�

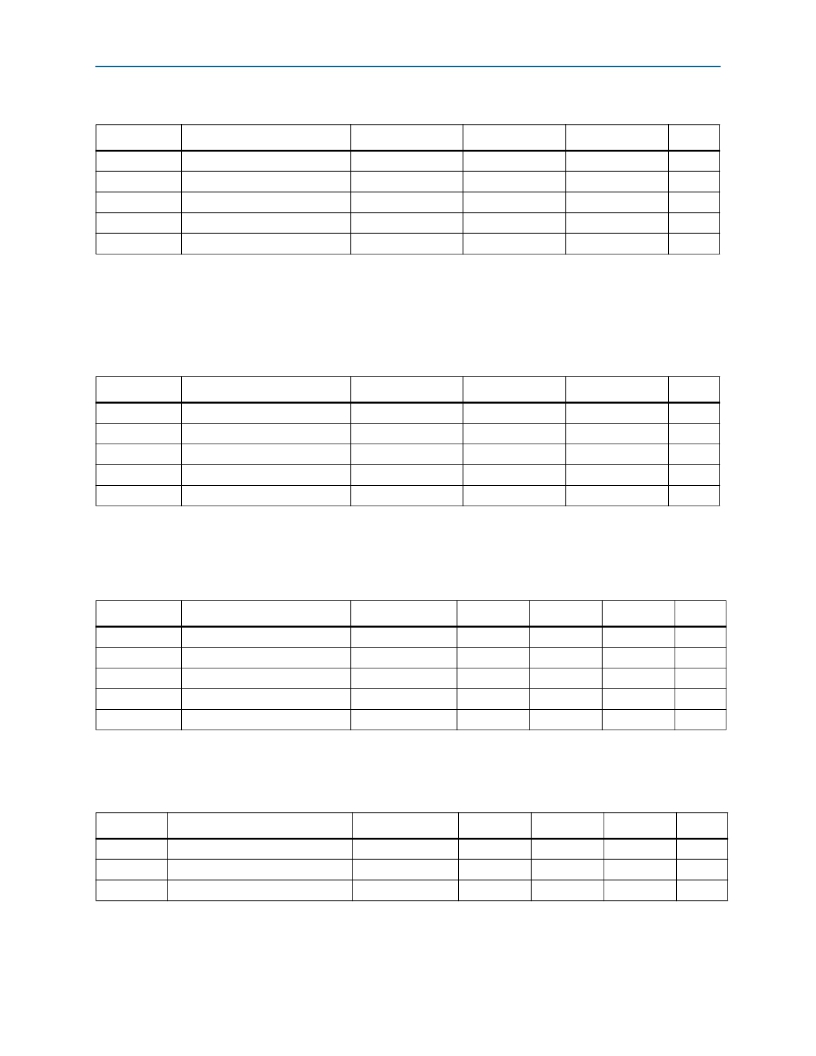

�Table� 3–9.� 1.5-V� I/O� Specifications� for� MAX� V� Devices�

�3–7�

�Symbol�

�V� CCIO�

�V� IH�

�V� IL�

�V� OH�

�V� OL�

�Parameter�

�I/O� supply� voltage�

�High-level� input� voltage�

�Low-level� input� voltage�

�High-level� output� voltage�

�Low-level� output� voltage�

�Conditions�

�—�

�—�

�—�

�IOH� =� –2� mA� (1)�

�IOL� =� 2� mA� (1)�

�Minimum�

�1.425�

�0.65� � V� CCIO�

�–0.3�

�0.75� � V� CCIO�

�—�

�Maximum�

�1.575�

�V� CCIO� +� 0.3� (2)�

�0.35� � V� CCIO�

�—�

�0.25� � V� CCIO�

�Unit�

�V�

�V�

�V�

�V�

�V�

��(1)� This� specification� is� supported� across� all� the� programmable� drive� strength� settings� available� for� this� I/O� standard,� as� shown� in� the�

��(2)� This� maximum� V� IH� reflects� the� JEDEC� specification.� The� MAX� V� input� buffer� can� tolerate� a� V� IH� maximum� of� 4.0,� as� specified� by� the� V� I� parameter�

��Table� 3–10.� 1.2-V� I/O� Specifications� for� MAX� V� Devices�

�Symbol�

�V� CCIO�

�V� IH�

�V� IL�

�V� OH�

�V� OL�

�Parameter�

�I/O� supply� voltage�

�High-level� input� voltage�

�Low-level� input� voltage�

�High-level� output� voltage�

�Low-level� output� voltage�

�Conditions�

�—�

�—�

�—�

�IOH� =� –2� mA� (1)�

�IOL� =� 2� mA� (1)�

�Minimum�

�1.14�

�0.8� � V� CCIO�

�–0.3�

�0.75� � V� CCIO�

�—�

�Maximum�

�1.26�

�V� CCIO� +� 0.3�

�0.25� � V� CCIO�

�—�

�0.25� � V� CCIO�

�Unit�

�V�

�V�

�V�

�V�

�V�

��(1)� This� specification� is� supported� across� all� the� programmable� drive� strength� settings� available� for� this� I/O� standard,� as� shown� in� the�

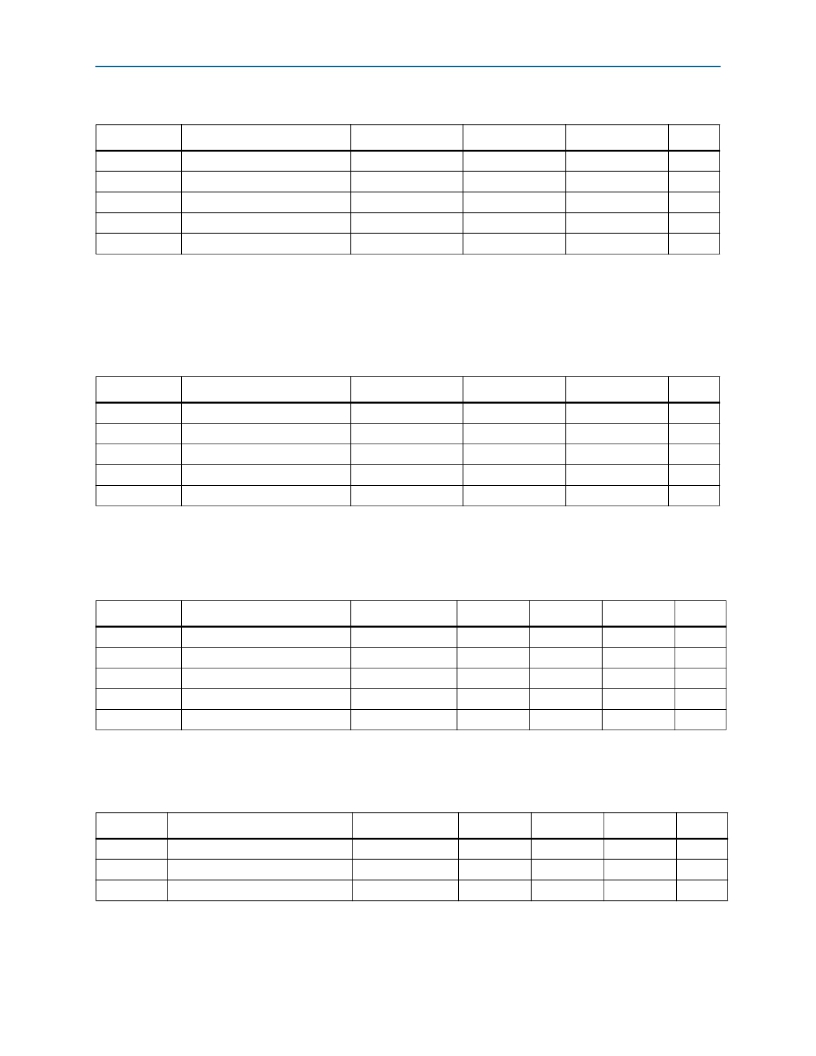

���Symbol�

�V� CCIO�

�V� IH�

�V� IL�

�V� OH�

�V� OL�

�Parameter�

�I/O� supply� voltage�

�High-level� input� voltage�

�Low-level� input� voltage�

�High-level� output� voltage�

�Low-level� output� voltage�

�Conditions�

�—�

�—�

�—�

�IOH� =� –500� μA�

�IOL� =� 1.5� mA�

�Minimum�

�3.0�

�0.5� � V� CCIO�

�–0.5�

�0.9� � V� CCIO�

�—�

�Typical�

�3.3�

�—�

�—�

�—�

�—�

�Maximum�

�3.6�

�V� CCIO� +� 0.5�

�0.3� � V� CCIO�

�—�

�0.1� � V� CCIO�

�Unit�

�V�

�V�

�V�

�V�

�V�

��(1)� 3.3-V� PCI� I/O� standard� is� only� supported� in� Bank� 3� of� the� 5M1270Z� and� 5M2210Z� devices.�

��Symbol�

�V� CCIO�

�V� OD�

�V� OS�

�Parameter�

�I/O� supply� voltage�

�Differential� output� voltage� swing�

�Output� offset� voltage�

�Conditions�

�—�

�—�

�—�

�Minimum�

�2.375�

�247�

�1.125�

�Typical�

�2.5�

�—�

�1.25�

�Maximum�

�2.625�

�600�

�1.375�

�Unit�

�V�

�mV�

�V�

��(1)� Supports� emulated� LVDS� output� using� a� three-resistor� network� (LVDS_E_3R).�

�May� 2011�

�Altera� Corporation�

��相关PDF资料 |

PDF描述 |

|---|---|

| VE-B4P-CX-B1 | CONVERTER MOD DC/DC 13.8V 75W |

| ECC13DRTN-S13 | CONN EDGECARD 26POS .100 EXTEND |

| ABC35DRYN-S13 | CONN EDGECARD 70POS .100 EXTEND |

| EEC07DRTN-S13 | CONN EDGECARD 14POS .100 EXTEND |

| EBC08DREH | CONN EDGECARD 16POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5M947P10-6P | 制造商:Amphenol Corporation 功能描述:71-310010-06P - Bulk |

| 5M947P14-19P | 制造商:Amphenol Corporation 功能描述:71-310014-19P - Bulk |

| 5M947P14-19PX | 制造商:Amphenol Corporation 功能描述:71-310014-19I - Bulk |

| 5M947P16-26P | 制造商:Amphenol Corporation 功能描述:71-310016-26P - Bulk |

| 5M947P18-32P | 制造商:Amphenol Corporation 功能描述:71-310018-32P - Bulk |

发布紧急采购,3分钟左右您将得到回复。