- 您现在的位置:买卖IC网 > PDF目录2058 > 5P49EE602NLGI (IDT, Integrated Device Technology Inc)IC CLOCK GENERATOR 24QFN PDF资料下载

参数资料

| 型号: | 5P49EE602NLGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 21/26页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GENERATOR 24QFN |

| 标准包装: | 75 |

| 系列: | VersaClock™ |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVTTL,晶体 |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 120MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-VFQFN 裸露焊盘 |

| 供应商设备封装: | 24-QFN(4x4) |

| 包装: | 管件 |

| 其它名称: | 800-2525 |

IDT5P49EE602

VERSACLOCK LOW POWER CLOCK GENERATOR

EEPROM CLOCK GENERATOR

IDT VERSACLOCK LOW POWER CLOCK GENERATOR

4

IDT5P49EE602

REV L 072512

Note *: SEL pins should be controlled by 1.8V LVTTL logic; 3.3V tolerant.

Note 1: Outputs are user programmable to drive single-ended 1.8V/2.5V/3.3V LVTTL as indicated above.

Note 2: Default configuration CLK3=Buffered Reference output. All other outputs are off.

Note 3: Do not power up with SEL[1:0] = 00 (in Power down/Sleep mode).

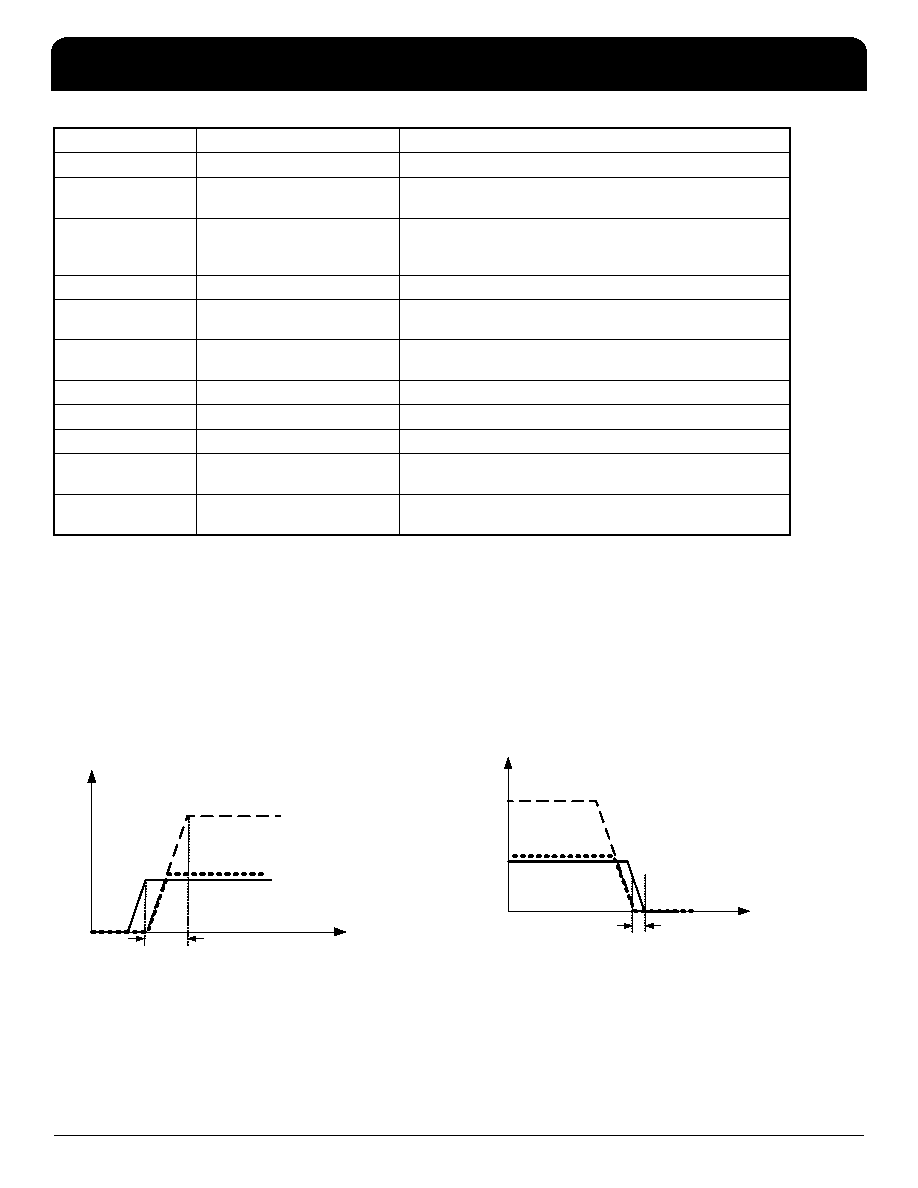

Ideal Power Up Sequence

Ideal Power Down Sequence

GND

13

Power

Connect to Ground.

VDD

14

Power

Device power supply. Connect to 1.8V.

OUT0

15

O

Adjustable

Configurable clock output 0. Single-ended output voltage levels

are register controlled by either VDDO1, VDDO2 or VDDO3.

VDDO3

16

Power

Device power supply. Connect to 1.8 to 3.3V. Using register

settings, select output voltage levels for OUT0/3/6/7/8/9.

VDDO3 must be equal or less than VDDO1.

SCLK

17

I

LVTTL

I2C clock. Logic levels set by VDDO1. 5V tolerant.

OUT4B

18

O

Adjustable

Configurable clock output 4B. Output voltage levels are

controlled by VDDO1.

OUT4A

19

O

Adjustable

Configurable clock output 4A. Output voltage levels are

controlled by VDDO1.

SDA

20

I/O

Open Drain

Bidirectional I2C data. Logic levels set by VDDO1. 5V tolerant.

VDD

21

Power

Device power supply. Connect to 1.8V.

GND

22

Power

Connect to Ground.

XIN/ REF

23

I

LVTTL

MHz CRYSTAL_IN -- Reference crystal input or external

reference clock input. Maximum clock input voltage is 1.8V.

XOUT

24

O

LVTTL

MHz CRYSTAL_OUT -- Reference crystal feedback. Float pin if

using reference input clock.

V

t

VDD, VDDx

VDDO1

VDDO2, VDDO3

1) VDD and VDDx must come up first, followed by VDDO

2) VDDO1 must come up within 1ms after VDD and VDDX come up

3) VDDO2/3 must be equal to, or lower than, VDDO1

4) VDD and VDDx have approx. the same ramp rate

5) VDDO1 and VDDO2/3 have approx. same ramp rate

1 ms

V

t

VDD, VDDx

VDDO1

1) VDDO must drop first, followed by VDD and VDDx

2) VDD and VDDx must come down within 1ms after VDDO1 comes down

3) VDDO2/3 must be equal to, or lower than, VDDO1

4) VDD and VDDx have approx. the same ramp rate

5) VDDO1 and VDDO2/3 have approx. same ramp rate

VDDO2, VDDO3

1 ms

相关PDF资料 |

PDF描述 |

|---|---|

| 5P49EE801NDGI | IC CLOCK GENERATOR 28QFN |

| 74ABT16240ADGG,518 | IC INVERTER QUAD 4-INPUT 48TSSOP |

| 74ABT16244ADGG,518 | IC BUFF DVR TRI-ST 16BIT 48TSSOP |

| 74ABT2240PW,118 | IC INVERTER DUAL 4-INPUT 20TSSOP |

| 74ABT620PW,118 | IC TRANSCVR 3ST 8BIT INV 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5P49EE602NLGI8 | 功能描述:时钟发生器及支持产品 VERSACLOCK LOW POWER PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 5P49EE605NLGI | 功能描述:锁相环 - PLL PROGRAMMABLE PLL LOW POWER RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| 5P49EE605NLGI8 | 制造商:Integrated Device Technology Inc 功能描述:VERSACLOCK LOW POWER CLOCK GENERATOR 制造商:Integrated Device Technology Inc 功能描述:24 QFN (GREEN) - Tape and Reel |

| 5P49EE801NDGI | 功能描述:时钟发生器及支持产品 VERSACLOCK LOW POWER PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 5P49EE801NDGI8 | 功能描述:时钟发生器及支持产品 VERSACLOCK LOW POWER PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。