- 您现在的位置:买卖IC网 > Datasheet目录299 > 71M6533G-IGTR/F (Maxim Integrated)IC ENERGY METER 3PH 100LQFP Datasheet资料下载

参数资料

| 型号: | 71M6533G-IGTR/F |

| 厂商: | Maxim Integrated |

| 文件页数: | 11/132页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METER 3PH 100LQFP |

| 标准包装: | 400 |

| 系列: | Single Converter Technology® |

| 输入阻抗: | 40 千欧 ~ 90 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 2V |

| 电压 - 低输入/输出: | 0.8V |

| 电流 - 电源: | 10mA |

| 电源电压: | 3 V ~ 3.6 V |

| 测量仪表类型: | 三相,中性相位 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页

�� �

�

�

�FDS_6533_6534_004�

�71M6533/G/H� and� 71M6534/H� Data� Sheet�

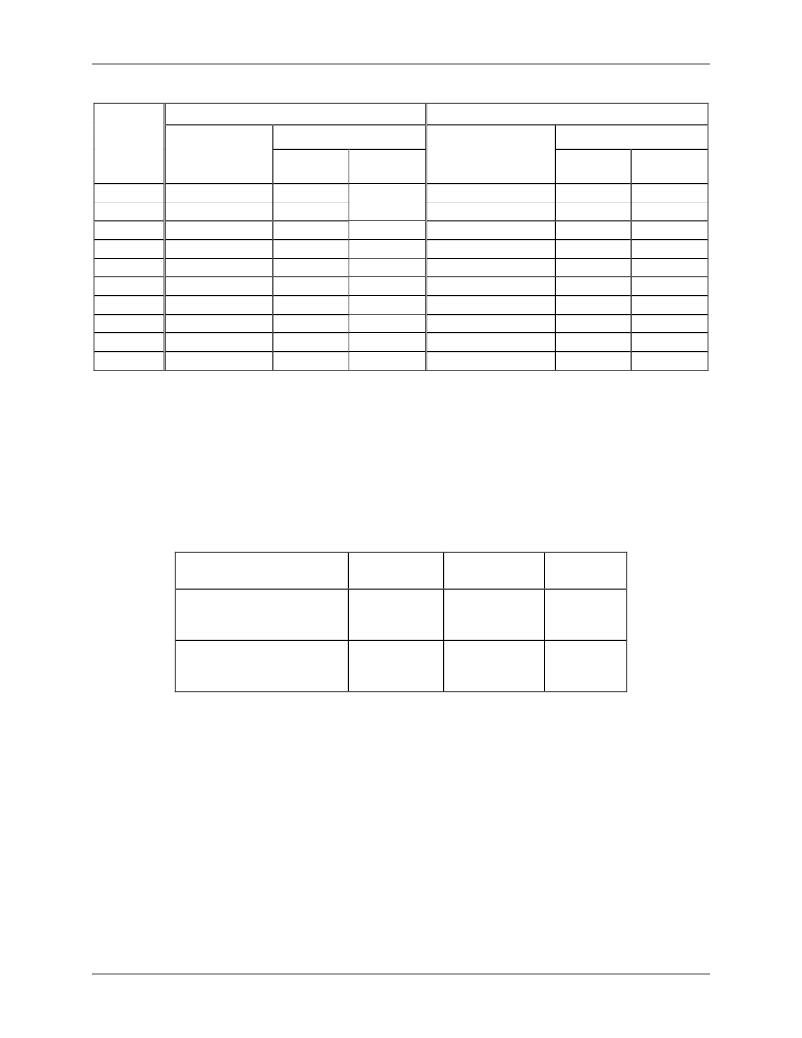

�Table� 1:� Signals� Selected� for� the� ADC� with� SLOTn_SEL� and� SLOTn_ALTSEL� (� MUX_DIV[3:0]� =� 7)�

�Regular� Slot�

�Alternate� Slot�

�Time�

�Slot�

�Register�

�Typical� Selections�

�Signal� Signal� for�

�Number� ADC�

�Register�

�Typical� Selections�

�Signal� Signal� for�

�Number� ADC�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�SLOT0_SEL[3:0]�

�SLOT1_SEL[3:0]�

�SLOT2_SEL[3:0]�

�SLOT3_SEL[3:0]�

�SLOT4_SEL[3:0]�

�SLOT5_SEL[3:0]�

�SLOT6_SEL[3:0]�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�IA�

�VA�

�IB�

�VB�

�IC�

�VC�

�ID�

�SLOT0_ALTSEL[3:0]�

�SLOT1_ALTSEL[3:0]�

�SLOT2_ALTSEL[3:0]�

�SLOT3_ALTSEL[3:0]�

�SLOT4_ALTSEL[3:0]�

�SLOT5_ALTSEL[3:0]�

�SLOT6_ALTSEL[3:0]�

�A�

�1�

�B�

�3�

�4�

�5�

�6�

�TEMP�

�VA�

�VBAT�

�VB�

�IC�

�VC�

�ID�

�SLOT7_SEL[3:0]�

�SLOT8_SEL[3:0]�

�SLOT9_SEL[3:0]�

�–�

�–�

�–�

�–�

�–�

�–�

�SLOT7_ALTSEL[3:0]�

�SLOT8_ALTSEL[3:0]�

�SLOT9_ALTSEL[3:0]�

�The� duration� of� each� multiplexer� state� depends� on� the� number� of� ADC� samples� processed� by� the� FIR,�

�which� is� set� by� FIR_LEN[1:0]� .� Each� multiplexer� state� will� start� on� the� rising� edge� of� CK32.� FIR� conversions�

�require� 1,� 2,� or� 3� CK32� cycles.� The� number� of� CK32� cycles� is� determined� by� FIR_LEN[1:0]� .�

�1.2.3�

�A/D� Converter� (ADC)�

�A� single� delta-sigma� A/D� converter� digitizes� the� voltage� and� current� inputs� to� the� 71M6533/71M6534.� The�

�resolution� of� the� ADC� is� programmable� using� the� I/O� RAM� bits� M40MHZ� and� M26MHZ� (see� Table� 2� ).� The�

�CE� code� must� be� tailored� for� use� with� the� selected� ADC� resolution.�

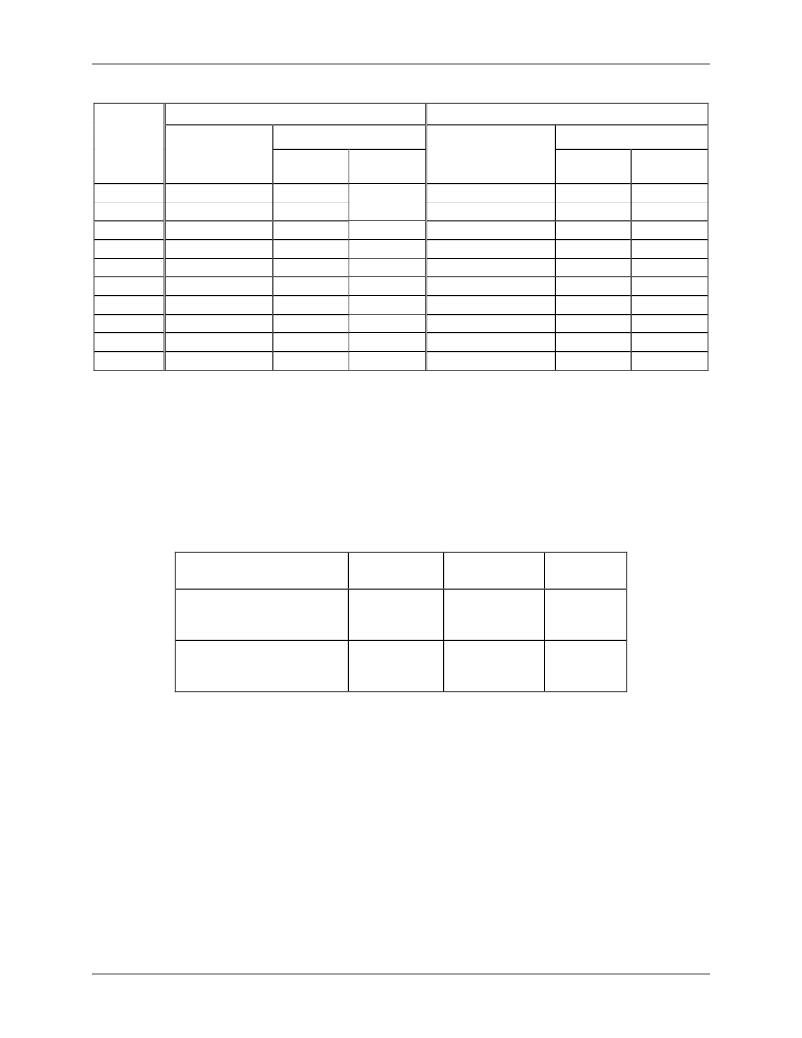

�Table� 2:� ADC� Resolution�

�Setting� for� [� M40MHZ,�

�M26MHZ� ]�

�[00],� [10]� or� [11]�

�[01]�

�FIR_LEN[1:0]�

�0�

�1�

�2�

�0�

�1�

�2�

�FIR� CE�

�Cycles�

�138�

�288�

�384�

�186�

�384�

�588�

�Resolution�

�18� bits�

�21� bits�

�22� bits�

�19� bits�

�22� bits�

�24� bits�

�Initiation� of� each� ADC� conversion� is� controlled� by� MUX_CTRL� as� described� in� Section� 1.1.1� .� At� the� end� of�

�each� ADC� conversion,� the� FIR� filter� output� data� is� stored� into� the� CE� RAM� location� determined� by� the� MUX�

�selection.�

�1.2.4�

�FIR� Filter�

�The� finite� impulse� response� filter� is� an� integral� part� of� the� ADC� and� it� is� optimized� for� use� with� the� multiplexer.�

�The� purpose� of� the� FIR� filter� is� to� decimate� the� ADC� output� to� the� desired� resolution.� At� the� end� of� each�

�ADC� conversion,� the� output� data� is� stored� into� the� fixed� CE� RAM� location� determined� by� the� multiplexer�

�selection� as� shown� in� Table� 3� .� FIR� data� is� stored� LSB� justified,� but� shifted� left� by� eight� bits.�

�Rev� 2�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| 71M6543F-IGT/F | IC ENERGY METERING |

| 71M6545-IGT/F | IC ENERGY METERING |

| 720-10007-00300 | CBL D-SUB 9PIN FMAL-25PIN FML 3M |

| 720-10010-00025 | CBL DSUB 9PIN FML-25PIN MAL .25M |

| 720-10020-00300 | CBL DSUB 9PIN FML-9PIN MALE 3M |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6533H | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6533H-IEL | 制造商:Maxim Integrated Products 功能描述:Metering Systems on a Chip - SoC Precision Energy Meter IC |

| 71M6533H-IEL/F | 制造商:Maxim Integrated Products 功能描述:Metering Systems on a Chip - SoC Precision Energy Meter IC |

| 71M6533H-IELR | 制造商:Maxim Integrated Products 功能描述:Metering Systems on a Chip - SoC Precision Energy Meter IC |

| 71M6533H-IELR/F | 制造商:Maxim Integrated Products 功能描述:Metering Systems on a Chip - SoC Precision Energy Meter IC |

发布紧急采购,3分钟左右您将得到回复。